|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

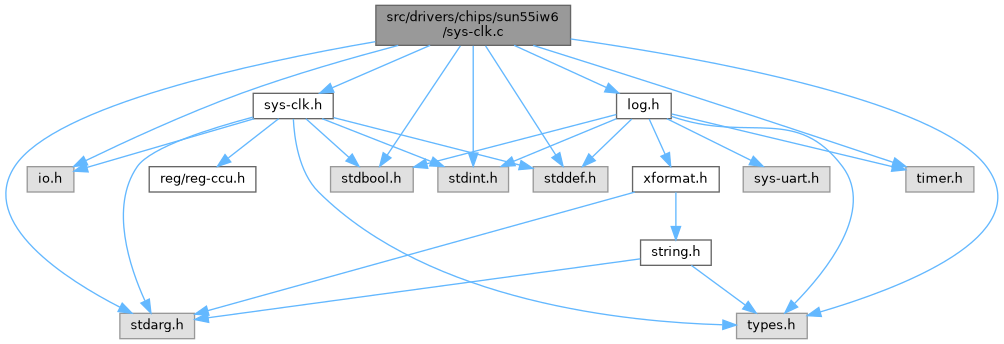

#include <io.h>#include <stdarg.h>#include <stdbool.h>#include <stddef.h>#include <stdint.h>#include <types.h>#include <timer.h>#include <log.h>#include <sys-clk.h>

Macros | |

| #define | CPU_UPDATE_OFFSET (26) |

| #define | CPU_LOCK_OFFSET (28) |

| #define | CPU_LOCK_ENABLE_OFFSET (29) |

Functions | |

| static void | enable_pll (uint32_t reg_addr, uint32_t n_factor) |

| Enables the PLL (Phase-Locked Loop) with a given factor. | |

| static void | set_pll_cpux_axi (void) |

| Configures the CPU and DSU PLLs, and sets the CPU-to-AXI divider. | |

| static void | set_apb (void) |

| Configures the APB clock source and divider. | |

| static void | set_pll_nsi (void) |

| Configures the NSI (Non-Shared Interface) clock source and gating. | |

| static void | set_pll_mbus (void) |

| Configures the MBUS (Memory Bus) clock source and gating. | |

| void | sunxi_clk_init (void) |

| Initializes the clocks for the Sunxi platform. | |

| void | sunxi_clk_dump () |

| Dump all clock-related register values. | |

| #define CPU_LOCK_ENABLE_OFFSET (29) |

| #define CPU_LOCK_OFFSET (28) |

| #define CPU_UPDATE_OFFSET (26) |

Enables the PLL (Phase-Locked Loop) with a given factor.

This function configures and enables the PLL by setting specific bits in the provided register address. The PLL configuration parameters such as n_factor, lock enable, and update offset are adjusted to match the desired PLL configuration. After configuring, the function waits for the PLL to lock and then performs a final check to ensure the lock is complete.

| reg_addr | The register address to configure the PLL. |

| n_factor | The PLL multiplier factor (used to set the PLL's frequency). Typically, this value will be used in the calculation: PLL Frequency = 24M * n / p / (m0 * m1). A specific n_factor value adjusts the PLL's output. |

|

static |

Configures the APB clock source and divider.

This function configures the APB1 clock source and sets its divider to a default value by modifying the appropriate control registers. It ensures the APB clock is sourced from the High-Speed Oscillator (HOSC) and sets the APB clock factor to its default value.

|

static |

Configures the CPU and DSU PLLs, and sets the CPU-to-AXI divider.

This function configures the PLLs for the CPU and DSU by calling the enable_pll function with predefined PLL multiplier factors. It also adjusts the CPU-to-AXI clock divider by modifying the corresponding register to control the clock speed and synchronization.

|

static |

Configures the MBUS (Memory Bus) clock source and gating.

This function first disables the MBUS clock gating, updates the MBUS clock divider, then sets the MBUS clock source to DDR PLL, and finally enables the MBUS clock. It waits for the updates to complete to ensure proper clock configuration.

|

static |

Configures the NSI (Non-Shared Interface) clock source and gating.

This function first disables the NSI clock gating, updates the NSI clock divider, then sets the NSI clock source to DDR PLL, and finally enables the NSI clock. It also waits for the updates to complete, ensuring that the clock configurations are applied correctly.

| void sunxi_clk_dump | ( | void | ) |

Dump all clock-related register values.

This function prints out all clock-related register values for debugging and observation.

| void sunxi_clk_init | ( | void | ) |

Initializes the clocks for the Sunxi platform.

Initialize the global clocks.

This function configures various clock sources for the CPU, AXI, APB, NSI, and MBUS based on the Sunxi platform's requirements. The function also prints debug messages to track the initialization process.

It performs the following tasks:

set_pll_cpux_axi() function.set_apb() function.set_pll_nsi() function.set_pll_mbus() function.