|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

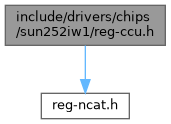

#include <reg-ncat.h>

Go to the source code of this file.

| #define AHB_CLK_REG 0x00000510 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define AHB_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define AHB_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define AHB_CLK_REG_CLK_SRC_SEL_PERI_600M_BUS 0b11 |

| #define AHB_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define AHB_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AHB_CLK_REG_FACTOR_N_1 0b00 |

| #define AHB_CLK_REG_FACTOR_N_2 0b01 |

| #define AHB_CLK_REG_FACTOR_N_4 0b10 |

| #define AHB_CLK_REG_FACTOR_N_8 0b11 |

| #define AHB_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define AHB_CLK_REG_FACTOR_N_OFFSET 8 |

| #define AHB_GATE_EN_REG 0x00000e04 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_CLEAR_MASK 0x80000000 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_DISABLE_AUTO_CLOCK_GATE 0b0 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_ENABLE_AUTO_CLOCK_GATE 0b1 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_OFFSET 31 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_CLEAR_MASK 0x10000000 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_OFFSET 28 |

| #define AHB_GATE_EN_REG_GMAC_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000100 |

| #define AHB_GATE_EN_REG_GMAC_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_GMAC_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_GMAC_AHB_GATE_SW_CFG_OFFSET 8 |

| #define AHB_GATE_EN_REG_GMAC_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00002000 |

| #define AHB_GATE_EN_REG_GMAC_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_GMAC_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_GMAC_MBUS_AHB_GATE_SW_CFG_OFFSET 13 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_CLEAR_MASK 0x20000000 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_DISABLE_AUTO_CLOCK_GATE 0b0 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_ENABLE_AUTO_CLOCK_GATE 0b1 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_OFFSET 29 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000020 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_OFFSET 5 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000400 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_OFFSET 10 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000040 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_OFFSET 6 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000800 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_OFFSET 11 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000080 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_OFFSET 7 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00001000 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_OFFSET 12 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000010 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_OFFSET 4 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000200 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_OFFSET 9 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000002 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_OFFSET 1 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000004 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_OFFSET 2 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000008 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_OFFSET 3 |

| #define APB0_CLK_REG 0x00000520 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define APB0_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define APB0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB0_CLK_REG_CLK_SRC_SEL_PERI_600M_BUS 0b11 |

| #define APB0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define APB0_CLK_REG_FACTOR_N_1 0b00 |

| #define APB0_CLK_REG_FACTOR_N_2 0b01 |

| #define APB0_CLK_REG_FACTOR_N_4 0b10 |

| #define APB0_CLK_REG_FACTOR_N_8 0b11 |

| #define APB0_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define APB0_CLK_REG_FACTOR_N_OFFSET 8 |

| #define APB1_CLK_REG 0x00000524 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define APB1_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define APB1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB1_CLK_REG_CLK_SRC_SEL_PERI_600M_BUS 0b11 |

| #define APB1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define APB1_CLK_REG_FACTOR_N_1 0b00 |

| #define APB1_CLK_REG_FACTOR_N_2 0b01 |

| #define APB1_CLK_REG_FACTOR_N_4 0b10 |

| #define APB1_CLK_REG_FACTOR_N_8 0b11 |

| #define APB1_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define APB1_CLK_REG_FACTOR_N_OFFSET 8 |

| #define APB_UART_CLK_REG 0x00000528 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_AUDIO_CKO_DIV2 0b100 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b010 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLK32K 0b001 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_PERI_600M_BUS 0b011 |

| #define APB_UART_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB_UART_CLK_REG_FACTOR_M_OFFSET 0 |

| #define APB_UART_CLK_REG_FACTOR_N_1 0b00 |

| #define APB_UART_CLK_REG_FACTOR_N_2 0b01 |

| #define APB_UART_CLK_REG_FACTOR_N_4 0b10 |

| #define APB_UART_CLK_REG_FACTOR_N_8 0b11 |

| #define APB_UART_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define APB_UART_CLK_REG_FACTOR_N_OFFSET 8 |

| #define AUDIO_CODEC_ADC_CLK_REG 0x00000a54 |

| #define AUDIO_CODEC_ADC_CLK_REG_AUDIO_CODEC_ADC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define AUDIO_CODEC_ADC_CLK_REG_AUDIO_CODEC_ADC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define AUDIO_CODEC_ADC_CLK_REG_AUDIO_CODEC_ADC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define AUDIO_CODEC_ADC_CLK_REG_AUDIO_CODEC_ADC_CLK_GATING_OFFSET 31 |

| #define AUDIO_CODEC_ADC_CLK_REG_CLK_SRC_SEL_AUDIOPLL1X 0b0 |

| #define AUDIO_CODEC_ADC_CLK_REG_CLK_SRC_SEL_AUDIOPLL4X 0b1 |

| #define AUDIO_CODEC_ADC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define AUDIO_CODEC_ADC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define AUDIO_CODEC_ADC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000000f |

| #define AUDIO_CODEC_ADC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AUDIO_CODEC_BGR_REG 0x00000a5c |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_CLEAR_MASK 0x00000001 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_MASK 0b0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_OFFSET 0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_PASS 0b1 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_ASSERT 0b0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_CLEAR_MASK 0x00010000 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_DE_ASSERT 0b1 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_OFFSET 16 |

| #define AUDIO_CODEC_DAC_CLK_REG 0x00000a50 |

| #define AUDIO_CODEC_DAC_CLK_REG_AUDIO_CODEC_DAC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define AUDIO_CODEC_DAC_CLK_REG_AUDIO_CODEC_DAC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define AUDIO_CODEC_DAC_CLK_REG_AUDIO_CODEC_DAC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define AUDIO_CODEC_DAC_CLK_REG_AUDIO_CODEC_DAC_CLK_GATING_OFFSET 31 |

| #define AUDIO_CODEC_DAC_CLK_REG_CLK_SRC_SEL_AUDIOPLL1X 0b0 |

| #define AUDIO_CODEC_DAC_CLK_REG_CLK_SRC_SEL_AUDIOPLL4X 0b1 |

| #define AUDIO_CODEC_DAC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define AUDIO_CODEC_DAC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define AUDIO_CODEC_DAC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000000f |

| #define AUDIO_CODEC_DAC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AUDIOPLL_GATE_EN_REG 0x00000e14 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_AUTO_GATE_EN_AUTO 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_AUTO_GATE_EN_CLEAR_MASK 0x00000008 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_AUTO_GATE_EN_OFFSET 3 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_GATE_SW_CFG_CLEAR_MASK 0x00080000 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_GATE_SW_CFG_DISABLE 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_GATE_SW_CFG_ENABLE 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL1X_GATE_SW_CFG_OFFSET 19 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_AUTO_GATE_EN_AUTO 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_AUTO_GATE_EN_CLEAR_MASK 0x00000010 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_AUTO_GATE_EN_OFFSET 4 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_GATE_SW_CFG_CLEAR_MASK 0x00100000 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_GATE_SW_CFG_DISABLE 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_GATE_SW_CFG_ENABLE 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL4X_GATE_SW_CFG_OFFSET 20 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_AUTO_GATE_EN_AUTO 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_AUTO_GATE_EN_OFFSET 0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_GATE_SW_CFG_DISABLE 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_GATE_SW_CFG_ENABLE 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV2_GATE_SW_CFG_OFFSET 16 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_AUTO_GATE_EN_AUTO 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_AUTO_GATE_EN_CLEAR_MASK 0x00000002 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_AUTO_GATE_EN_OFFSET 1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_GATE_SW_CFG_DISABLE 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_GATE_SW_CFG_ENABLE 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV3_GATE_SW_CFG_OFFSET 17 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_AUTO_GATE_EN_AUTO 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_AUTO_GATE_EN_CLEAR_MASK 0x00000004 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_AUTO_GATE_EN_OFFSET 2 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_GATE_SW_CFG_DISABLE 0b0 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_GATE_SW_CFG_ENABLE 0b1 |

| #define AUDIOPLL_GATE_EN_REG_AUDIOPLL_DIV5_GATE_SW_CFG_OFFSET 18 |

| #define AUDIOPLL_GATE_STAT_REG 0x00000e2c |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL1X_GATE_STAT_CLEAR_MASK 0x00080000 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL1X_GATE_STAT_DISABLE 0b0 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL1X_GATE_STAT_ENABLE 0b1 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL1X_GATE_STAT_OFFSET 19 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL4X_GATE_STAT_CLEAR_MASK 0x00100000 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL4X_GATE_STAT_DISABLE 0b0 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL4X_GATE_STAT_ENABLE 0b1 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL4X_GATE_STAT_OFFSET 20 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV2_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV2_GATE_STAT_DISABLE 0b0 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV2_GATE_STAT_ENABLE 0b1 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV2_GATE_STAT_OFFSET 16 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV3_GATE_STAT_CLEAR_MASK 0x00020000 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV3_GATE_STAT_DISABLE 0b0 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV3_GATE_STAT_ENABLE 0b1 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV3_GATE_STAT_OFFSET 17 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV5_GATE_STAT_CLEAR_MASK 0x00040000 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV5_GATE_STAT_DISABLE 0b0 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV5_GATE_STAT_ENABLE 0b1 |

| #define AUDIOPLL_GATE_STAT_REG_AUDIOPLL_DIV5_GATE_STAT_OFFSET 18 |

| #define AVS_CLK_REG 0x00000740 |

| #define AVS_CLK_REG_AVS_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define AVS_CLK_REG_AVS_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define AVS_CLK_REG_AVS_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define AVS_CLK_REG_AVS_CLK_GATING_OFFSET 31 |

| #define CAN_BGR_REG 0x0000075c |

| #define CAN_BGR_REG_CAN0_GATING_CLEAR_MASK 0x00000001 |

| #define CAN_BGR_REG_CAN0_GATING_MASK 0b0 |

| #define CAN_BGR_REG_CAN0_GATING_OFFSET 0 |

| #define CAN_BGR_REG_CAN0_GATING_PASS 0b1 |

| #define CAN_BGR_REG_CAN0_RST_ASSERT 0b0 |

| #define CAN_BGR_REG_CAN0_RST_CLEAR_MASK 0x00010000 |

| #define CAN_BGR_REG_CAN0_RST_DE_ASSERT 0b1 |

| #define CAN_BGR_REG_CAN0_RST_OFFSET 16 |

| #define CAN_BGR_REG_CAN1_GATING_CLEAR_MASK 0x00000002 |

| #define CAN_BGR_REG_CAN1_GATING_MASK 0b0 |

| #define CAN_BGR_REG_CAN1_GATING_OFFSET 1 |

| #define CAN_BGR_REG_CAN1_GATING_PASS 0b1 |

| #define CAN_BGR_REG_CAN1_RST_ASSERT 0b0 |

| #define CAN_BGR_REG_CAN1_RST_CLEAR_MASK 0x00020000 |

| #define CAN_BGR_REG_CAN1_RST_DE_ASSERT 0b1 |

| #define CAN_BGR_REG_CAN1_RST_OFFSET 17 |

| #define CCM_SPIF_CTRL_ENABLE (0x1 << 31) |

| #define CCM_SPIF_CTRL_HOSC (0x0 << 24) |

| #define CCM_SPIF_CTRL_M | ( | x | ) | ((x) -1) |

| #define CCM_SPIF_CTRL_N | ( | x | ) | ((x) << 8) |

| #define CCM_SPIF_CTRL_PERI CCM_SPIF_CTRL_PERI400M |

| #define CCM_SPIF_CTRL_PERI300M (0x2 << 24) |

| #define CCM_SPIF_CTRL_PERI400M (0x1 << 24) |

| #define CCU_APB0_CFG_GREG (SUNXI_CCU_BASE + APB0_CLK_REG) |

| #define CCU_APB1_CFG_GREG (SUNXI_CCU_BASE + APB1_CLK_REG) |

| #define CCU_AUDIO_CODEC_BGR_REG (SUNXI_CCU_BASE + AUDIO_CODEC_BGR_REG) |

| #define CCU_AVS_CLK_REG (SUNXI_CCU_BASE + AVS_CLK_REG) |

| #define CCU_CE_BGR_REG (SUNXI_CCU_BASE + CE_BGR_REG) |

| #define CCU_CE_CLK_REG (SUNXI_CCU_BASE + CE_CLK_REG) |

| #define CCU_CLK24M_GATE_EN_REG (SUNXI_CCU_BASE + CLK24M_GATE_EN_REG) |

| #define CCU_CLK_SEL_REG (SUNXI_CCU_BASE + GPADC_CLK_SEL_REG) |

| #define CCU_CPUX_AXI_CFG_REG (SUNXI_CCU_BASE + CPU_CLK_REG) |

| #define CCU_DMA_BGR_REG (SUNXI_CCU_BASE + DMA_BGR_REG) |

| #define CCU_DRAM_BGR_REG (SUNXI_CCU_BASE + DRAM_BGR_REG) |

| #define CCU_DRAM_CLK_REG (SUNXI_CCU_BASE + DRAM_CLK_REG) |

| #define CCU_E907_CFG_REG (SUNXI_CCU_BASE + E907_CLK_REG) |

| #define CCU_FAN_GATE_REG 0x00000f30 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLEAR_MASK 0x00000002 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_OFFSET 1 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLEAR_MASK 0x00000004 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_OFFSET 2 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLEAR_MASK 0x00000001 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_OFFSET 0 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLEAR_MASK 0x00000008 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_OFFSET 3 |

| #define CCU_FAN_REG 0x00000f3c |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLEAR_MASK 0x00200000 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_OFFSET 21 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLEAR_MASK 0x00000007 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK16M_FROM_PERI_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK25M_FROM_PERI_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_OFFSET 0 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_PCLK 0b110 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLEAR_MASK 0x00400000 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_OFFSET 22 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLEAR_MASK 0x00000038 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK16M_FROM_PERI_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK25M_FROM_PERI_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_OFFSET 3 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_PCLK 0b110 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLEAR_MASK 0x00800000 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_OFFSET 23 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLEAR_MASK 0x000001c0 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK16M_FROM_PERI_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK25M_FROM_PERI_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_OFFSET 6 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_PCLK 0b110 |

| #define CCU_GPADC_BGR_REG (SUNXI_CCU_BASE + GPADC_BGR_REG) |

| #define CCU_MBUS_CFG_REG (SUNXI_CCU_BASE + MBUS_CLK_REG) |

| #define CCU_MBUS_MST_CLK_GATING_REG (SUNXI_CCU_BASE + MBUS_MAT_CLK_GATING_REG) |

| #define CCU_PLL_AUDIO0_PAT0_REG (SUNXI_CCU_BASE + PLL_AUDIO_PAT0_CTRL_REG) |

| #define CCU_PLL_AUDIO_CTRL_REG (SUNXI_CCU_BASE + PLL_AUDIO_CTRL_REG) |

| #define CCU_PLL_CPUX_CTRL_REG (SUNXI_CCU_BASE + PLL_CPU_CTRL_REG) |

| #define CCU_PLL_DDR0_CTRL_REG (SUNXI_CCU_BASE + PLL_DDR_CTRL_REG) |

| #define CCU_PLL_PERI0_CTRL_REG (SUNXI_CCU_BASE + PLL_PERI_CTRL_REG) |

| #define CCU_PLL_VIDEO_CTRL_REG (SUNXI_CCU_BASE + PLL_VIDEO_CTRL_REG) |

| #define CCU_PSI_AHB1_AHB2_CFG_REG (SUNXI_CCU_BASE + AHB_CLK_REG) |

| #define CCU_SDMMC0_CLK_REG (SUNXI_CCU_BASE + SMHC0_CLK_REG) |

| #define CCU_SDMMC1_CLK_REG (SUNXI_CCU_BASE + SMHC1_CLK_REG) |

| #define CCU_SDMMC2_CLK_REG (SUNXI_CCU_BASE + 0x838) |

| #define CCU_SEC_SWITCH_REG 0x00000f00 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_CLEAR_MASK 0x00000002 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_OFFSET 1 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_SECURE 0b0 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_CLEAR_MASK 0x00000004 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_OFFSET 2 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_SECURE 0b0 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_CLEAR_MASK 0x00000001 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_OFFSET 0 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_SECURE 0b0 |

| #define CCU_SMHC0_BGR_REG (SUNXI_CCU_BASE + SMHC_BGR_REG) |

| #define CCU_SPI0_CLK_REG (SUNXI_CCU_BASE + SPI0_CLK_REG) |

| #define CCU_SPI1_CLK_REG (SUNXI_CCU_BASE + SPI1_CLK_REG) |

| #define CCU_SPI_BGR_CLK_REG (SUNXI_CCU_BASE + SPI_BGR_REG) |

| #define CCU_USB0_CLK_REG (SUNXI_CCU_BASE + USB0_CLK_REG) |

| #define CCU_USB_BGR_REG (SUNXI_CCU_BASE + USB_BGR_REG) |

| #define CCU_VERSION_REG 0x00000ff0 |

| #define CCU_VERSION_REG_CCU_MAIN_VERSION_CLEAR_MASK 0xffff0000 |

| #define CCU_VERSION_REG_CCU_MAIN_VERSION_OFFSET 16 |

| #define CCU_VERSION_REG_CCU_SUB_VERSION_CLEAR_MASK 0x0000ffff |

| #define CCU_VERSION_REG_CCU_SUB_VERSION_OFFSET 0 |

| #define CE_BGR_REG 0x0000068c |

| #define CE_BGR_REG_CE_GATING_CLEAR_MASK 0x00000001 |

| #define CE_BGR_REG_CE_GATING_MASK 0b0 |

| #define CE_BGR_REG_CE_GATING_OFFSET 0 |

| #define CE_BGR_REG_CE_GATING_PASS 0b1 |

| #define CE_BGR_REG_CE_RST_ASSERT 0b0 |

| #define CE_BGR_REG_CE_RST_CLEAR_MASK 0x00010000 |

| #define CE_BGR_REG_CE_RST_DE_ASSERT 0b1 |

| #define CE_BGR_REG_CE_RST_OFFSET 16 |

| #define CE_BGR_REG_CE_SYS_GATING_CLEAR_MASK 0x00000002 |

| #define CE_BGR_REG_CE_SYS_GATING_MASK 0b0 |

| #define CE_BGR_REG_CE_SYS_GATING_OFFSET 1 |

| #define CE_BGR_REG_CE_SYS_GATING_PASS 0b1 |

| #define CE_BGR_REG_CE_SYS_RST_ASSERT 0b0 |

| #define CE_BGR_REG_CE_SYS_RST_CLEAR_MASK 0x00020000 |

| #define CE_BGR_REG_CE_SYS_RST_DE_ASSERT 0b1 |

| #define CE_BGR_REG_CE_SYS_RST_OFFSET 17 |

| #define CE_CLK_REG 0x00000680 |

| #define CE_CLK_REG_CE_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CE_CLK_REG_CE_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CE_CLK_REG_CE_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CE_CLK_REG_CE_CLK_GATING_OFFSET 31 |

| #define CE_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CE_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CE_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CE_CLK_REG_CLK_SRC_SEL_PERI_300M 0b010 |

| #define CE_CLK_REG_CLK_SRC_SEL_PERI_400M 0b001 |

| #define CE_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000000f |

| #define CE_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CE_USE_PLATFORM_CLOCK_FUNC |

| #define CLK24M_GATE_EN_REG 0x00000e0c |

| #define CLK24M_GATE_EN_REG_GPADC_24M_GATE_EN_CLEAR_MASK 0x00000004 |

| #define CLK24M_GATE_EN_REG_GPADC_24M_GATE_EN_DISABLE 0b0 |

| #define CLK24M_GATE_EN_REG_GPADC_24M_GATE_EN_ENABLE 0b1 |

| #define CLK24M_GATE_EN_REG_GPADC_24M_GATE_EN_OFFSET 2 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_CLEAR_MASK 0x00000008 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_DISABLE 0b0 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_ENABLE 0b1 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_OFFSET 3 |

| #define CLK24M_GATE_EN_REG_USB_24M_GATE_EN_CLEAR_MASK 0x00000001 |

| #define CLK24M_GATE_EN_REG_USB_24M_GATE_EN_DISABLE 0b0 |

| #define CLK24M_GATE_EN_REG_USB_24M_GATE_EN_ENABLE 0b1 |

| #define CLK24M_GATE_EN_REG_USB_24M_GATE_EN_OFFSET 0 |

| #define CLK27M_FAN_REG 0x00000f34 |

| #define CLK27M_FAN_REG_CLK27M_DIV0_CLEAR_MASK 0x0000001f |

| #define CLK27M_FAN_REG_CLK27M_DIV0_OFFSET 0 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_1 0b00 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_2 0b01 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_4 0b10 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_8 0b11 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_CLEAR_MASK 0x00000300 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_OFFSET 8 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLEAR_MASK 0x80000000 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLOCK_IS_OFF 0b0 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLOCK_IS_ON 0b1 |

| #define CLK27M_FAN_REG_CLK27M_EN_OFFSET 31 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_CLEAR_MASK 0x03000000 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_CSIPLL1X 0b001 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_OFFSET 24 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_PERI_300M 0b010 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_VIDEOPLL1X 0b000 |

| #define CLK_FAN_REG 0x00000f38 |

| #define CLK_FAN_REG_PCLK_DIV1_CLEAR_MASK 0x000003e0 |

| #define CLK_FAN_REG_PCLK_DIV1_OFFSET 5 |

| #define CLK_FAN_REG_PCLK_DIV_CLEAR_MASK 0x0000001f |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLEAR_MASK 0x80000000 |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLOCK_IS_OFF 0b0 |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLOCK_IS_ON 0b1 |

| #define CLK_FAN_REG_PCLK_DIV_EN_OFFSET 31 |

| #define CLK_FAN_REG_PCLK_DIV_OFFSET 0 |

| #define CPU_CFG_BGR_REG 0x0000050c |

| #define CPU_CFG_BGR_REG_CPU_CFG_GATING_CLEAR_MASK 0x00000001 |

| #define CPU_CFG_BGR_REG_CPU_CFG_GATING_MASK 0b0 |

| #define CPU_CFG_BGR_REG_CPU_CFG_GATING_OFFSET 0 |

| #define CPU_CFG_BGR_REG_CPU_CFG_GATING_PASS 0b1 |

| #define CPU_CFG_BGR_REG_CPU_CFG_RST_ASSERT 0b0 |

| #define CPU_CFG_BGR_REG_CPU_CFG_RST_CLEAR_MASK 0x00010000 |

| #define CPU_CFG_BGR_REG_CPU_CFG_RST_DE_ASSERT 0b1 |

| #define CPU_CFG_BGR_REG_CPU_CFG_RST_OFFSET 16 |

| #define CPU_CLK_REG 0x00000500 |

| #define CPU_CLK_REG_CPU_AXI_DIV_CFG_CLEAR_MASK 0x00000300 |

| #define CPU_CLK_REG_CPU_AXI_DIV_CFG_OFFSET 8 |

| #define CPU_CLK_REG_CPU_CLK_SEL_CLEAR_MASK 0x07000000 |

| #define CPU_CLK_REG_CPU_CLK_SEL_CLK16M_RC 0b010 |

| #define CPU_CLK_REG_CPU_CLK_SEL_CLK32K 0b001 |

| #define CPU_CLK_REG_CPU_CLK_SEL_CPUPLL_P 0b011 |

| #define CPU_CLK_REG_CPU_CLK_SEL_HOSC 0b000 |

| #define CPU_CLK_REG_CPU_CLK_SEL_OFFSET 24 |

| #define CPU_CLK_REG_CPU_CLK_SEL_PERI_600M_BUS 0b100 |

| #define CPU_CLK_REG_CPU_CLK_SEL_PERI_800M 0b101 |

| #define CPU_CLK_REG_PLL_CPU_OUT_EXT_DIVP_1 0b00 |

| #define CPU_CLK_REG_PLL_CPU_OUT_EXT_DIVP_2 0b01 |

| #define CPU_CLK_REG_PLL_CPU_OUT_EXT_DIVP_4 0b10 |

| #define CPU_CLK_REG_PLL_CPU_OUT_EXT_DIVP_CLEAR_MASK 0x00030000 |

| #define CPU_CLK_REG_PLL_CPU_OUT_EXT_DIVP_OFFSET 16 |

| #define CPU_GATING_REG 0x00000504 |

| #define CPU_GATING_REG_C0_CPUX_RESET_ASSERT 0b0 |

| #define CPU_GATING_REG_C0_CPUX_RESET_CLEAR_MASK 0x00000010 |

| #define CPU_GATING_REG_C0_CPUX_RESET_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_C0_CPUX_RESET_OFFSET 4 |

| #define CPU_GATING_REG_C1_CPUX_RESET_ASSERT 0b0 |

| #define CPU_GATING_REG_C1_CPUX_RESET_CLEAR_MASK 0x00000020 |

| #define CPU_GATING_REG_C1_CPUX_RESET_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_C1_CPUX_RESET_OFFSET 5 |

| #define CPU_GATING_REG_CPU_CLK_GATING_CLEAR_MASK 0x00000001 |

| #define CPU_GATING_REG_CPU_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CPU_GATING_REG_CPU_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CPU_GATING_REG_CPU_CLK_GATING_OFFSET 0 |

| #define CPU_GATING_REG_CPU_GATING_FIELD_CLEAR_MASK 0xffff0000 |

| #define CPU_GATING_REG_CPU_GATING_FIELD_OFFSET 16 |

| #define CPU_GATING_REG_CPU_IPMC_SOFT_RSTN_ASSERT 0b0 |

| #define CPU_GATING_REG_CPU_IPMC_SOFT_RSTN_CLEAR_MASK 0x00001000 |

| #define CPU_GATING_REG_CPU_IPMC_SOFT_RSTN_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_CPU_IPMC_SOFT_RSTN_OFFSET 12 |

| #define CPU_GATING_REG_CPU_SOFT_RSTN_ASSERT 0b0 |

| #define CPU_GATING_REG_CPU_SOFT_RSTN_CLEAR_MASK 0x00000002 |

| #define CPU_GATING_REG_CPU_SOFT_RSTN_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_CPU_SOFT_RSTN_OFFSET 1 |

| #define CPU_GATING_REG_CPU_SYS_APB_SOFT_RSTN_ASSERT 0b0 |

| #define CPU_GATING_REG_CPU_SYS_APB_SOFT_RSTN_CLEAR_MASK 0x00000004 |

| #define CPU_GATING_REG_CPU_SYS_APB_SOFT_RSTN_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_CPU_SYS_APB_SOFT_RSTN_OFFSET 2 |

| #define CPU_GATING_REG_H_RESET_CLEAR_MASK 0x00000100 |

| #define CPU_GATING_REG_H_RESET_OFFSET 8 |

| #define CPU_GATING_REG_PIC_SOFT_RSTN_ASSERT 0b0 |

| #define CPU_GATING_REG_PIC_SOFT_RSTN_CLEAR_MASK 0x00000008 |

| #define CPU_GATING_REG_PIC_SOFT_RSTN_DE_ASSERT 0b1 |

| #define CPU_GATING_REG_PIC_SOFT_RSTN_OFFSET 3 |

| #define CPUPLL_GATE_EN_REG 0x00000e24 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_AUTO_GATE_EN_AUTO 0b0 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_AUTO_GATE_EN_OFFSET 0 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_GATE_SW_CFG_DISABLE 0b0 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_GATE_SW_CFG_ENABLE 0b1 |

| #define CPUPLL_GATE_EN_REG_CPUPLL_GATE_SW_CFG_OFFSET 16 |

| #define CPUPLL_GATE_STAT_REG 0x00000e3c |

| #define CPUPLL_GATE_STAT_REG_CPUPLL_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define CPUPLL_GATE_STAT_REG_CPUPLL_GATE_STAT_DISABLE 0b0 |

| #define CPUPLL_GATE_STAT_REG_CPUPLL_GATE_STAT_ENABLE 0b1 |

| #define CPUPLL_GATE_STAT_REG_CPUPLL_GATE_STAT_OFFSET 16 |

| #define CSI_BGR_REG 0x00000c2c |

| #define CSI_BGR_REG_CSI_GATING_CLEAR_MASK 0x00000001 |

| #define CSI_BGR_REG_CSI_GATING_MASK 0b0 |

| #define CSI_BGR_REG_CSI_GATING_OFFSET 0 |

| #define CSI_BGR_REG_CSI_GATING_PASS 0b1 |

| #define CSI_BGR_REG_CSI_RST_ASSERT 0b0 |

| #define CSI_BGR_REG_CSI_RST_CLEAR_MASK 0x00010000 |

| #define CSI_BGR_REG_CSI_RST_DE_ASSERT 0b1 |

| #define CSI_BGR_REG_CSI_RST_OFFSET 16 |

| #define CSI_CLK_REG 0x00000c04 |

| #define CSI_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_CLK_REG_CLK_SRC_SEL_CSIPLL4X 0b011 |

| #define CSI_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_CLK_REG_CLK_SRC_SEL_PERI_300M 0b000 |

| #define CSI_CLK_REG_CLK_SRC_SEL_PERI_400M 0b001 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VIDEOPLL4X 0b010 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_CLK_REG_CSI_CLK_GATING_OFFSET 31 |

| #define CSI_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER0_CLK_REG 0x00000c08 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_CSIPLL4X 0b001 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_PERIPLL2X 0b011 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_VIDEOPLL4X 0b010 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_1 0b00 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_2 0b01 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_4 0b10 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_8 0b11 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSI_MASTER1_CLK_REG 0x00000c0c |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_CSIPLL4X 0b001 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_PERIPLL2X 0b011 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_VIDEOPLL4X 0b010 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_1 0b00 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_2 0b01 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_4 0b10 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_8 0b11 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSI_MASTER2_CLK_REG 0x00000c10 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_CSIPLL4X 0b001 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_PERIPLL2X 0b011 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_VIDEOPLL4X 0b010 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER2_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER2_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_1 0b00 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_2 0b01 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_4 0b10 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_8 0b11 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSIPLL_GATE_EN_REG 0x00000e1c |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_AUTO_GATE_EN_AUTO 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_AUTO_GATE_EN_OFFSET 0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_GATE_SW_CFG_DISABLE 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_GATE_SW_CFG_ENABLE 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL1X_GATE_SW_CFG_OFFSET 16 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_AUTO_GATE_EN_AUTO 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_AUTO_GATE_EN_CLEAR_MASK 0x00000002 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_AUTO_GATE_EN_OFFSET 1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_GATE_SW_CFG_DISABLE 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_GATE_SW_CFG_ENABLE 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL2X_GATE_SW_CFG_OFFSET 17 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_AUTO_GATE_EN_AUTO 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_AUTO_GATE_EN_CLEAR_MASK 0x00000004 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_AUTO_GATE_EN_OFFSET 2 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_GATE_SW_CFG_DISABLE 0b0 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_GATE_SW_CFG_ENABLE 0b1 |

| #define CSIPLL_GATE_EN_REG_CSIPLL4X_GATE_SW_CFG_OFFSET 18 |

| #define CSIPLL_GATE_STAT_REG 0x00000e34 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL1X_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL1X_GATE_STAT_DISABLE 0b0 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL1X_GATE_STAT_ENABLE 0b1 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL1X_GATE_STAT_OFFSET 16 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL2X_GATE_STAT_CLEAR_MASK 0x00020000 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL2X_GATE_STAT_DISABLE 0b0 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL2X_GATE_STAT_ENABLE 0b1 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL2X_GATE_STAT_OFFSET 17 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL4X_GATE_STAT_CLEAR_MASK 0x00040000 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL4X_GATE_STAT_DISABLE 0b0 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL4X_GATE_STAT_ENABLE 0b1 |

| #define CSIPLL_GATE_STAT_REG_CSIPLL4X_GATE_STAT_OFFSET 18 |

| #define DBGSYS_BGR_REG 0x0000078c |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_CLEAR_MASK 0x00000001 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_MASK 0b0 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_OFFSET 0 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_PASS 0b1 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_ASSERT 0b0 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_CLEAR_MASK 0x00010000 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_DE_ASSERT 0b1 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_OFFSET 16 |

| #define DDRPLL_GATE_EN_REG 0x00000e20 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_AUTO_GATE_EN_AUTO 0b0 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_AUTO_GATE_EN_OFFSET 0 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_GATE_SW_CFG_DISABLE 0b0 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_GATE_SW_CFG_ENABLE 0b1 |

| #define DDRPLL_GATE_EN_REG_DDRPLL_GATE_SW_CFG_OFFSET 16 |

| #define DDRPLL_GATE_STAT_REG 0x00000e38 |

| #define DDRPLL_GATE_STAT_REG_DDRPLL_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define DDRPLL_GATE_STAT_REG_DDRPLL_GATE_STAT_DISABLE 0b0 |

| #define DDRPLL_GATE_STAT_REG_DDRPLL_GATE_STAT_ENABLE 0b1 |

| #define DDRPLL_GATE_STAT_REG_DDRPLL_GATE_STAT_OFFSET 16 |

| #define DE_BGR_REG 0x0000060c |

| #define DE_BGR_REG_DE_GATING_CLEAR_MASK 0x00000001 |

| #define DE_BGR_REG_DE_GATING_MASK 0b0 |

| #define DE_BGR_REG_DE_GATING_OFFSET 0 |

| #define DE_BGR_REG_DE_GATING_PASS 0b1 |

| #define DE_BGR_REG_DE_RST_ASSERT 0b0 |

| #define DE_BGR_REG_DE_RST_CLEAR_MASK 0x00010000 |

| #define DE_BGR_REG_DE_RST_DE_ASSERT 0b1 |

| #define DE_BGR_REG_DE_RST_OFFSET 16 |

| #define DE_CLK_REG 0x00000600 |

| #define DE_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define DE_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define DE_CLK_REG_CLK_SRC_SEL_PERI_300M 0b0 |

| #define DE_CLK_REG_CLK_SRC_SEL_VIDEOPLL1X 0b1 |

| #define DE_CLK_REG_DE_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DE_CLK_REG_DE_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DE_CLK_REG_DE_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DE_CLK_REG_DE_CLK_GATING_OFFSET 31 |

| #define DE_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define DE_CLK_REG_FACTOR_M_OFFSET 0 |

| #define DMA_BGR_REG 0x0000070c |

| #define DMA_BGR_REG_NDMA_GATING_CLEAR_MASK 0x00000002 |

| #define DMA_BGR_REG_NDMA_GATING_MASK 0b0 |

| #define DMA_BGR_REG_NDMA_GATING_OFFSET 1 |

| #define DMA_BGR_REG_NDMA_GATING_PASS 0b1 |

| #define DMA_BGR_REG_NDMA_RST_ASSERT 0b0 |

| #define DMA_BGR_REG_NDMA_RST_CLEAR_MASK 0x00020000 |

| #define DMA_BGR_REG_NDMA_RST_DE_ASSERT 0b1 |

| #define DMA_BGR_REG_NDMA_RST_OFFSET 17 |

| #define DMA_BGR_REG_SGDMA_GATING_CLEAR_MASK 0x00000001 |

| #define DMA_BGR_REG_SGDMA_GATING_MASK 0b0 |

| #define DMA_BGR_REG_SGDMA_GATING_OFFSET 0 |

| #define DMA_BGR_REG_SGDMA_GATING_PASS 0b1 |

| #define DMA_BGR_REG_SGDMA_RST_ASSERT 0b0 |

| #define DMA_BGR_REG_SGDMA_RST_CLEAR_MASK 0x00010000 |

| #define DMA_BGR_REG_SGDMA_RST_DE_ASSERT 0b1 |

| #define DMA_BGR_REG_SGDMA_RST_OFFSET 16 |

| #define DMA_GATING_BASE CCU_DMA_BGR_REG |

| #define DPSS_TOP_BGR_REG 0x00000abc |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_GATING_CLEAR_MASK 0x00000001 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_GATING_MASK 0b0 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_GATING_OFFSET 0 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_GATING_PASS 0b1 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_RST_ASSERT 0b0 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_RST_CLEAR_MASK 0x00010000 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_RST_DE_ASSERT 0b1 |

| #define DPSS_TOP_BGR_REG_DPSS_TOP_RST_OFFSET 16 |

| #define DRAM_BGR_REG 0x0000080c |

| #define DRAM_BGR_REG_DRAM_GATING_CLEAR_MASK 0x00000001 |

| #define DRAM_BGR_REG_DRAM_GATING_MASK 0b0 |

| #define DRAM_BGR_REG_DRAM_GATING_OFFSET 0 |

| #define DRAM_BGR_REG_DRAM_GATING_PASS 0b1 |

| #define DRAM_BGR_REG_DRAM_RST_ASSERT 0b0 |

| #define DRAM_BGR_REG_DRAM_RST_CLEAR_MASK 0x00010000 |

| #define DRAM_BGR_REG_DRAM_RST_DE_ASSERT 0b1 |

| #define DRAM_BGR_REG_DRAM_RST_OFFSET 16 |

| #define DRAM_CLK_REG 0x00000800 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_OFFSET 31 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_CLEAR_MASK 0x07000000 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_DDRPLL 0b001 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_HOSC 0b000 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_OFFSET 24 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI_800M 0b011 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERIPLL2X 0b010 |

| #define DRAM_CLK_REG_DRAM_DIV1_CLEAR_MASK 0x0000001f |

| #define DRAM_CLK_REG_DRAM_DIV1_OFFSET 0 |

| #define DRAM_CLK_REG_DRAM_DIV2_1 0b00 |

| #define DRAM_CLK_REG_DRAM_DIV2_2 0b01 |

| #define DRAM_CLK_REG_DRAM_DIV2_4 0b10 |

| #define DRAM_CLK_REG_DRAM_DIV2_8 0b11 |

| #define DRAM_CLK_REG_DRAM_DIV2_CLEAR_MASK 0x00000300 |

| #define DRAM_CLK_REG_DRAM_DIV2_OFFSET 8 |

| #define DRAM_CLK_REG_DRAM_UPD_CLEAR_MASK 0x08000000 |

| #define DRAM_CLK_REG_DRAM_UPD_INVALID 0b0 |

| #define DRAM_CLK_REG_DRAM_UPD_OFFSET 27 |

| #define DRAM_CLK_REG_DRAM_UPD_VALID 0b1 |

| #define E907_CFG_BASE (0x06010000) |

| #define E907_CFG_GATING_BIT (0) |

| #define E907_CFG_GATING_RESET_BASE (SUNXI_CCU_BASE + 0xd0c) |

| #define E907_CFG_RST_BIT (16) |

| #define E907_CLK_GATING_BIT (0) |

| #define E907_CLK_REG 0x00000d00 |

| #define E907_CLK_REG_E907_AXI_DIV_CFG_CLEAR_MASK 0x00000300 |

| #define E907_CLK_REG_E907_AXI_DIV_CFG_OFFSET 8 |

| #define E907_CLK_REG_E907_CLK_SEL_CLEAR_MASK 0x07000000 |

| #define E907_CLK_REG_E907_CLK_SEL_CLK16M_RC 0b010 |

| #define E907_CLK_REG_E907_CLK_SEL_CLK32K 0b001 |

| #define E907_CLK_REG_E907_CLK_SEL_CPUPLL 0b101 |

| #define E907_CLK_REG_E907_CLK_SEL_HOSC 0b000 |

| #define E907_CLK_REG_E907_CLK_SEL_OFFSET 24 |

| #define E907_CLK_REG_E907_CLK_SEL_PERI_600M 0b011 |

| #define E907_CLK_REG_E907_CLK_SEL_PERI_800M 0b100 |

| #define E907_CLK_REG_E907_DIV_CFG_CLEAR_MASK 0x0000001f |

| #define E907_CLK_REG_E907_DIV_CFG_OFFSET 0 |

| #define E907_GATING_RST_FIELD (0x16aa) |

| #define E907_GATING_RST_REG 0x00000d04 |

| #define E907_GATING_RST_REG_E907_CLK_GATING_CLEAR_MASK 0x00000001 |

| #define E907_GATING_RST_REG_E907_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define E907_GATING_RST_REG_E907_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define E907_GATING_RST_REG_E907_CLK_GATING_OFFSET 0 |

| #define E907_GATING_RST_REG_E907_CORE_SOFT_RSTN_ASSERT 0b0 |

| #define E907_GATING_RST_REG_E907_CORE_SOFT_RSTN_CLEAR_MASK 0x00000008 |

| #define E907_GATING_RST_REG_E907_CORE_SOFT_RSTN_DE_ASSERT 0b1 |

| #define E907_GATING_RST_REG_E907_CORE_SOFT_RSTN_OFFSET 3 |

| #define E907_GATING_RST_REG_E907_GATING_RST_FIELD_CLEAR_MASK 0xffff0000 |

| #define E907_GATING_RST_REG_E907_GATING_RST_FIELD_OFFSET 16 |

| #define E907_GATING_RST_REG_E907_SOFT_RSTN_ASSERT 0b0 |

| #define E907_GATING_RST_REG_E907_SOFT_RSTN_CLEAR_MASK 0x00000002 |

| #define E907_GATING_RST_REG_E907_SOFT_RSTN_DE_ASSERT 0b1 |

| #define E907_GATING_RST_REG_E907_SOFT_RSTN_OFFSET 1 |

| #define E907_GATING_RST_REG_RISCV_SYS_APB_SOFT_RSTN_ASSERT 0b0 |

| #define E907_GATING_RST_REG_RISCV_SYS_APB_SOFT_RSTN_CLEAR_MASK 0x00000004 |

| #define E907_GATING_RST_REG_RISCV_SYS_APB_SOFT_RSTN_DE_ASSERT 0b1 |

| #define E907_GATING_RST_REG_RISCV_SYS_APB_SOFT_RSTN_OFFSET 2 |

| #define E907_SOFT_RST_BIT (1) |

| #define E907_STA_ADD_REG (E907_CFG_BASE + 0x0204) |

| #define E907_SYS_APB_SOFT_RST_BIT (2) |

| #define E907_SYS_GATING_RESET_BASE (SUNXI_CCU_BASE + 0xd04) |

| #define FRE_DET_CTRL_REG 0x00000f08 |

| #define FRE_DET_CTRL_REG_DET_TIME_CLEAR_MASK 0x000001f0 |

| #define FRE_DET_CTRL_REG_DET_TIME_OFFSET 4 |

| #define FRE_DET_CTRL_REG_ERROR_FLAG_CLEAR_MASK 0x80000000 |

| #define FRE_DET_CTRL_REG_ERROR_FLAG_ERROR 0b1 |

| #define FRE_DET_CTRL_REG_ERROR_FLAG_OFFSET 31 |

| #define FRE_DET_CTRL_REG_ERROR_FLAG_WRITE_0_TO_CLEAR 0b0 |

| #define FRE_DET_CTRL_REG_FRE_DET_FUN_EN_CLEAR_MASK 0x00000001 |

| #define FRE_DET_CTRL_REG_FRE_DET_FUN_EN_DISABLE 0b0 |

| #define FRE_DET_CTRL_REG_FRE_DET_FUN_EN_ENABLE 0b1 |

| #define FRE_DET_CTRL_REG_FRE_DET_FUN_EN_OFFSET 0 |

| #define FRE_DET_CTRL_REG_FRE_DET_IRQ_EN_CLEAR_MASK 0x00000002 |

| #define FRE_DET_CTRL_REG_FRE_DET_IRQ_EN_DISABLE 0b0 |

| #define FRE_DET_CTRL_REG_FRE_DET_IRQ_EN_ENABLE 0b1 |

| #define FRE_DET_CTRL_REG_FRE_DET_IRQ_EN_OFFSET 1 |

| #define FRE_DOWN_LIM_REG 0x00000f10 |

| #define FRE_DOWN_LIM_REG_FRE_DOWN_LIM_CLEAR_MASK 0xffffffff |

| #define FRE_DOWN_LIM_REG_FRE_DOWN_LIM_OFFSET 0 |

| #define FRE_UP_LIM_REG 0x00000f0c |

| #define FRE_UP_LIM_REG_FRE_UP_LIM_CLEAR_MASK 0xffffffff |

| #define FRE_UP_LIM_REG_FRE_UP_LIM_OFFSET 0 |

| #define G2D_BGR_REG 0x0000063c |

| #define G2D_BGR_REG_G2D_GATING_CLEAR_MASK 0x00000001 |

| #define G2D_BGR_REG_G2D_GATING_MASK 0b0 |

| #define G2D_BGR_REG_G2D_GATING_OFFSET 0 |

| #define G2D_BGR_REG_G2D_GATING_PASS 0b1 |

| #define G2D_BGR_REG_G2D_RST_ASSERT 0b0 |

| #define G2D_BGR_REG_G2D_RST_CLEAR_MASK 0x00010000 |

| #define G2D_BGR_REG_G2D_RST_DE_ASSERT 0b1 |

| #define G2D_BGR_REG_G2D_RST_OFFSET 16 |

| #define G2D_CLK_REG 0x00000630 |

| #define G2D_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define G2D_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define G2D_CLK_REG_CLK_SRC_SEL_PERI_300M 0b0 |

| #define G2D_CLK_REG_CLK_SRC_SEL_VIDEOPLL1X 0b1 |

| #define G2D_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define G2D_CLK_REG_FACTOR_M_OFFSET 0 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define G2D_CLK_REG_G2D_CLK_GATING_OFFSET 31 |

| #define GET_SPIF_CLK_SOURECS | ( | x | ) | (x == CCM_SPIF_CTRL_PERI400M ? 400000000 : 300000000) |

| #define GMAC_25M_CLK_REG 0x00000970 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_GATING_OFFSET 31 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SRC_GATING_CLEAR_MASK 0x40000000 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SRC_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SRC_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SRC_GATING_OFFSET 30 |

| #define GMAC_BGR_REG 0x0000097c |

| #define GMAC_BGR_REG_GMAC_GATING_CLEAR_MASK 0x00000001 |

| #define GMAC_BGR_REG_GMAC_GATING_MASK 0b0 |

| #define GMAC_BGR_REG_GMAC_GATING_OFFSET 0 |

| #define GMAC_BGR_REG_GMAC_GATING_PASS 0b1 |

| #define GMAC_BGR_REG_GMAC_RST_ASSERT 0b0 |

| #define GMAC_BGR_REG_GMAC_RST_CLEAR_MASK 0x00010000 |

| #define GMAC_BGR_REG_GMAC_RST_DE_ASSERT 0b1 |

| #define GMAC_BGR_REG_GMAC_RST_OFFSET 16 |

| #define GPADC_BGR_REG 0x000009ec |

| #define GPADC_BGR_REG_GPADC_GATING_CLEAR_MASK 0x00000001 |

| #define GPADC_BGR_REG_GPADC_GATING_MASK 0b0 |

| #define GPADC_BGR_REG_GPADC_GATING_OFFSET 0 |

| #define GPADC_BGR_REG_GPADC_GATING_PASS 0b1 |

| #define GPADC_BGR_REG_GPADC_RST_ASSERT 0b0 |

| #define GPADC_BGR_REG_GPADC_RST_CLEAR_MASK 0x00010000 |

| #define GPADC_BGR_REG_GPADC_RST_DE_ASSERT 0b1 |

| #define GPADC_BGR_REG_GPADC_RST_OFFSET 16 |

| #define GPADC_CLK_SEL_REG 0x00000f04 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_CLEAR_MASK 0x00700000 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC 0b101 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC_16 0b001 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC_2 0b100 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC_32 0b000 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC_4 0b011 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_HOSC_8 0b010 |

| #define GPADC_CLK_SEL_REG_GPADC_24M_CLK_SEL_OFFSET 20 |

| #define HSTIMER_BGR_REG 0x0000073c |

| #define HSTIMER_BGR_REG_HSTIMER_GATING_CLEAR_MASK 0x00000001 |

| #define HSTIMER_BGR_REG_HSTIMER_GATING_MASK 0b0 |

| #define HSTIMER_BGR_REG_HSTIMER_GATING_OFFSET 0 |

| #define HSTIMER_BGR_REG_HSTIMER_GATING_PASS 0b1 |

| #define HSTIMER_BGR_REG_HSTIMER_RST_ASSERT 0b0 |

| #define HSTIMER_BGR_REG_HSTIMER_RST_CLEAR_MASK 0x00010000 |

| #define HSTIMER_BGR_REG_HSTIMER_RST_DE_ASSERT 0b1 |

| #define HSTIMER_BGR_REG_HSTIMER_RST_OFFSET 16 |

| #define I2S0_CLK_REG 0x00000a10 |

| #define I2S0_CLK_REG_CLK_SRC_SEL_AUDIOPLL1X 0b0 |

| #define I2S0_CLK_REG_CLK_SRC_SEL_AUDIOPLL4X 0b1 |

| #define I2S0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define I2S0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define I2S0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000000f |

| #define I2S0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define I2S0_CLK_REG_I2S0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define I2S0_CLK_REG_I2S0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define I2S0_CLK_REG_I2S0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define I2S0_CLK_REG_I2S0_CLK_GATING_OFFSET 31 |

| #define I2S_BGR_REG 0x00000a2c |

| #define I2S_BGR_REG_I2S0_GATING_CLEAR_MASK 0x00000001 |

| #define I2S_BGR_REG_I2S0_GATING_MASK 0b0 |

| #define I2S_BGR_REG_I2S0_GATING_OFFSET 0 |

| #define I2S_BGR_REG_I2S0_GATING_PASS 0b1 |

| #define I2S_BGR_REG_I2S0_RST_ASSERT 0b0 |

| #define I2S_BGR_REG_I2S0_RST_CLEAR_MASK 0x00010000 |

| #define I2S_BGR_REG_I2S0_RST_DE_ASSERT 0b1 |

| #define I2S_BGR_REG_I2S0_RST_OFFSET 16 |

| #define IPMC_CLK_REG 0x000004fc |

| #define IPMC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IPMC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IPMC_CLK_REG_IPMC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IPMC_CLK_REG_IPMC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IPMC_CLK_REG_IPMC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IPMC_CLK_REG_IPMC_CLK_GATING_OFFSET 31 |

| #define MBUS_CLK_REG 0x00000540 |

| #define MBUS_CLK_REG_MBUS_RST_ASSERT 0b0 |

| #define MBUS_CLK_REG_MBUS_RST_CLEAR_MASK 0x40000000 |

| #define MBUS_CLK_REG_MBUS_RST_DE_ASSERT 0b1 |

| #define MBUS_CLK_REG_MBUS_RST_OFFSET 30 |

| #define MBUS_MAT_CLK_GATING_REG 0x00000804 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_OFFSET 18 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MCLK_EN_CLEAR_MASK 0x00000004 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MCLK_EN_OFFSET 2 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_CSI_MCLK_EN_CLEAR_MASK 0x00000100 |

| #define MBUS_MAT_CLK_GATING_REG_CSI_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_CSI_MCLK_EN_OFFSET 8 |

| #define MBUS_MAT_CLK_GATING_REG_CSI_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MBUS_GATE_SW_CFG_OFFSET 16 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MCLK_EN_CLEAR_MASK 0x00000001 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MCLK_EN_OFFSET 0 |

| #define MBUS_MAT_CLK_GATING_REG_DMA_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_G2D_MCLK_EN_CLEAR_MASK 0x00000400 |

| #define MBUS_MAT_CLK_GATING_REG_G2D_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_G2D_MCLK_EN_OFFSET 10 |

| #define MBUS_MAT_CLK_GATING_REG_G2D_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_ISP_MCLK_EN_CLEAR_MASK 0x00000200 |

| #define MBUS_MAT_CLK_GATING_REG_ISP_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_ISP_MCLK_EN_OFFSET 9 |

| #define MBUS_MAT_CLK_GATING_REG_ISP_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00200000 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_OFFSET 21 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_OFFSET 17 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MCLK_EN_CLEAR_MASK 0x00000002 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MCLK_EN_MASK 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MCLK_EN_OFFSET 1 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00100000 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_OFFSET 20 |

| #define MBUS_MAT_CLK_GATING_REG_VID_OUT_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00080000 |

| #define MBUS_MAT_CLK_GATING_REG_VID_OUT_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VID_OUT_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VID_OUT_MBUS_GATE_SW_CFG_OFFSET 19 |

| #define MSGBOX_BGR_REG 0x0000071c |

| #define MSGBOX_BGR_REG_MSGBOX0_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_BGR_REG_MSGBOX0_GATING_MASK 0b0 |

| #define MSGBOX_BGR_REG_MSGBOX0_GATING_OFFSET 0 |

| #define MSGBOX_BGR_REG_MSGBOX0_GATING_PASS 0b1 |

| #define MSGBOX_BGR_REG_MSGBOX0_RST_ASSERT 0b0 |

| #define MSGBOX_BGR_REG_MSGBOX0_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_BGR_REG_MSGBOX0_RST_DE_ASSERT 0b1 |

| #define MSGBOX_BGR_REG_MSGBOX0_RST_OFFSET 16 |

| #define MSGBOX_BGR_REG_MSGBOX1_GATING_CLEAR_MASK 0x00000002 |

| #define MSGBOX_BGR_REG_MSGBOX1_GATING_MASK 0b0 |

| #define MSGBOX_BGR_REG_MSGBOX1_GATING_OFFSET 1 |

| #define MSGBOX_BGR_REG_MSGBOX1_GATING_PASS 0b1 |

| #define MSGBOX_BGR_REG_MSGBOX1_RST_ASSERT 0b0 |

| #define MSGBOX_BGR_REG_MSGBOX1_RST_CLEAR_MASK 0x00020000 |

| #define MSGBOX_BGR_REG_MSGBOX1_RST_DE_ASSERT 0b1 |

| #define MSGBOX_BGR_REG_MSGBOX1_RST_OFFSET 17 |

| #define NPU_BGR_REG 0x000006ec |

| #define NPU_BGR_REG_NPU_GATING_CLEAR_MASK 0x00000001 |

| #define NPU_BGR_REG_NPU_GATING_MASK 0b0 |

| #define NPU_BGR_REG_NPU_GATING_OFFSET 0 |

| #define NPU_BGR_REG_NPU_GATING_PASS 0b1 |

| #define NPU_BGR_REG_NPU_RST_ASSERT 0b0 |

| #define NPU_BGR_REG_NPU_RST_CLEAR_MASK 0x00010000 |

| #define NPU_BGR_REG_NPU_RST_DE_ASSERT 0b1 |

| #define NPU_BGR_REG_NPU_RST_OFFSET 16 |

| #define NPU_CLK_REG 0x000006e0 |

| #define NPU_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define NPU_CLK_REG_CLK_SRC_SEL_NPUPLL4X 0b10 |

| #define NPU_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define NPU_CLK_REG_CLK_SRC_SEL_PERI_600M 0b01 |

| #define NPU_CLK_REG_CLK_SRC_SEL_PERI_800M 0b00 |

| #define NPU_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define NPU_CLK_REG_FACTOR_M_OFFSET 0 |

| #define NPU_CLK_REG_NPU_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define NPU_CLK_REG_NPU_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define NPU_CLK_REG_NPU_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define NPU_CLK_REG_NPU_CLK_GATING_OFFSET 31 |

| #define NPU_GATING_REG 0x000006e4 |

| #define NPU_GATING_REG_NPU_GLB_CLKG_BPS_CFG_BYPASS 0b1 |

| #define NPU_GATING_REG_NPU_GLB_CLKG_BPS_CFG_CLEAR_MASK 0x00000010 |

| #define NPU_GATING_REG_NPU_GLB_CLKG_BPS_CFG_OFFSET 4 |

| #define NPU_GATING_REG_NPU_GLB_CLKG_BPS_CFG_RELEASE 0b0 |

| #define NPU_GATING_REG_NPU_SW_RESET_CFG_ASSERT 0b1 |

| #define NPU_GATING_REG_NPU_SW_RESET_CFG_CLEAR_MASK 0x00000100 |

| #define NPU_GATING_REG_NPU_SW_RESET_CFG_DE_ASSERT 0b0 |

| #define NPU_GATING_REG_NPU_SW_RESET_CFG_OFFSET 8 |

| #define NPUPLL_GATE_EN_REG 0x00000e40 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_AUTO_GATE_EN_AUTO 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_AUTO_GATE_EN_OFFSET 0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_GATE_SW_CFG_DISABLE 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_GATE_SW_CFG_ENABLE 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL1X_GATE_SW_CFG_OFFSET 16 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_AUTO_GATE_EN_AUTO 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_AUTO_GATE_EN_CLEAR_MASK 0x00000002 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_AUTO_GATE_EN_OFFSET 1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_GATE_SW_CFG_DISABLE 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_GATE_SW_CFG_ENABLE 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL2X_GATE_SW_CFG_OFFSET 17 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_AUTO_GATE_EN_AUTO 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_AUTO_GATE_EN_CLEAR_MASK 0x00000004 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_AUTO_GATE_EN_OFFSET 2 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_GATE_SW_CFG_DISABLE 0b0 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_GATE_SW_CFG_ENABLE 0b1 |

| #define NPUPLL_GATE_EN_REG_NPUPLL4X_GATE_SW_CFG_OFFSET 18 |

| #define NPUPLL_GATE_STAT_REG 0x00000e44 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL1X_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL1X_GATE_STAT_DISABLE 0b0 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL1X_GATE_STAT_ENABLE 0b1 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL1X_GATE_STAT_OFFSET 16 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL2X_GATE_STAT_CLEAR_MASK 0x00020000 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL2X_GATE_STAT_DISABLE 0b0 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL2X_GATE_STAT_ENABLE 0b1 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL2X_GATE_STAT_OFFSET 17 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL4X_GATE_STAT_CLEAR_MASK 0x00040000 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL4X_GATE_STAT_DISABLE 0b0 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL4X_GATE_STAT_ENABLE 0b1 |

| #define NPUPLL_GATE_STAT_REG_NPUPLL4X_GATE_STAT_OFFSET 18 |

| #define PERIPLL_GATE_EN_REG 0x00000e08 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_AUTO_GATE_EN_CLEAR_MASK 0x00000008 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_AUTO_GATE_EN_OFFSET 3 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_GATE_SW_CFG_CLEAR_MASK 0x00080000 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_150M_GATE_SW_CFG_OFFSET 19 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_AUTO_GATE_EN_CLEAR_MASK 0x00000040 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_AUTO_GATE_EN_OFFSET 6 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_GATE_SW_CFG_CLEAR_MASK 0x00400000 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_160M_GATE_SW_CFG_OFFSET 22 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_AUTO_GATE_EN_CLEAR_MASK 0x00000001 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_AUTO_GATE_EN_OFFSET 0 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_200M_GATE_SW_CFG_OFFSET 16 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_ALL_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_ALL_CLEAR_MASK 0x00000020 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_ALL_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_ALL_OFFSET 5 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_CLEAR_MASK 0x00000010 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_AUTO_GATE_EN_OFFSET 4 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_ALL_CFG_CLEAR_MASK 0x00200000 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_ALL_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_ALL_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_ALL_CFG_OFFSET 21 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_SW_CFG_CLEAR_MASK 0x00100000 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_300M_GATE_SW_CFG_OFFSET 20 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_ALL_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_ALL_CLEAR_MASK 0x00000004 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_ALL_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_ALL_OFFSET 2 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_CLEAR_MASK 0x00000002 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_AUTO_GATE_EN_OFFSET 1 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_ALL_CFG_CLEAR_MASK 0x00040000 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_ALL_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_ALL_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_ALL_CFG_OFFSET 18 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_400M_GATE_SW_CFG_OFFSET 17 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_ALL_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_ALL_CLEAR_MASK 0x00000100 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_ALL_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_ALL_OFFSET 8 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_CLEAR_MASK 0x00000080 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_AUTO_GATE_EN_OFFSET 7 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_ALL_CFG_CLEAR_MASK 0x01000000 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_ALL_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_ALL_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_ALL_CFG_OFFSET 24 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_SW_CFG_CLEAR_MASK 0x00800000 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_480M_GATE_SW_CFG_OFFSET 23 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_AUTO_GATE_EN_CLEAR_MASK 0x00000200 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_AUTO_GATE_EN_OFFSET 9 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_GATE_SW_CFG_CLEAR_MASK 0x02000000 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_600M_GATE_SW_CFG_OFFSET 25 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_AUTO_GATE_EN_CLEAR_MASK 0x00000400 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_AUTO_GATE_EN_OFFSET 10 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_GATE_SW_CFG_CLEAR_MASK 0x04000000 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERI_800M_GATE_SW_CFG_OFFSET 26 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_AUTO_GATE_EN_AUTO 0b0 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_AUTO_GATE_EN_CLEAR_MASK 0x00000800 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_AUTO_GATE_EN_NO_AUTO 0b1 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_AUTO_GATE_EN_OFFSET 11 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_GATE_SW_CFG_CLEAR_MASK 0x08000000 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_GATE_SW_CFG_DISABLE 0b0 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_GATE_SW_CFG_ENABLE 0b1 |

| #define PERIPLL_GATE_EN_REG_PERIPLL2X_GATE_SW_CFG_OFFSET 27 |

| #define PERIPLL_GATE_STAT_REG 0x00000e28 |

| #define PERIPLL_GATE_STAT_REG_PERI_150M_GATE_STAT_CLEAR_MASK 0x00080000 |

| #define PERIPLL_GATE_STAT_REG_PERI_150M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_150M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_150M_GATE_STAT_OFFSET 19 |

| #define PERIPLL_GATE_STAT_REG_PERI_160M_GATE_STAT_CLEAR_MASK 0x00400000 |

| #define PERIPLL_GATE_STAT_REG_PERI_160M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_160M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_160M_GATE_STAT_OFFSET 22 |

| #define PERIPLL_GATE_STAT_REG_PERI_200M_GATE_STAT_CLEAR_MASK 0x00010000 |

| #define PERIPLL_GATE_STAT_REG_PERI_200M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_200M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_200M_GATE_STAT_OFFSET 16 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_ALL_STAT_CLEAR_MASK 0x00200000 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_ALL_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_ALL_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_ALL_STAT_OFFSET 21 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_STAT_CLEAR_MASK 0x00100000 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_300M_GATE_STAT_OFFSET 20 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_ALL_STAT_CLEAR_MASK 0x00040000 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_ALL_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_ALL_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_ALL_STAT_OFFSET 18 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_STAT_CLEAR_MASK 0x00020000 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_400M_GATE_STAT_OFFSET 17 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_ALL_STAT_CLEAR_MASK 0x01000000 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_ALL_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_ALL_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_ALL_STAT_OFFSET 24 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_STAT_CLEAR_MASK 0x00800000 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_480M_GATE_STAT_OFFSET 23 |

| #define PERIPLL_GATE_STAT_REG_PERI_600M_GATE_STAT_CLEAR_MASK 0x02000000 |

| #define PERIPLL_GATE_STAT_REG_PERI_600M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_600M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_600M_GATE_STAT_OFFSET 25 |

| #define PERIPLL_GATE_STAT_REG_PERI_800M_GATE_STAT_CLEAR_MASK 0x04000000 |

| #define PERIPLL_GATE_STAT_REG_PERI_800M_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERI_800M_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERI_800M_GATE_STAT_OFFSET 26 |

| #define PERIPLL_GATE_STAT_REG_PERIPLL2X_GATE_STAT_CLEAR_MASK 0x08000000 |

| #define PERIPLL_GATE_STAT_REG_PERIPLL2X_GATE_STAT_DISABLE 0b0 |

| #define PERIPLL_GATE_STAT_REG_PERIPLL2X_GATE_STAT_ENABLE 0b1 |

| #define PERIPLL_GATE_STAT_REG_PERIPLL2X_GATE_STAT_OFFSET 27 |

| #define PIC_CLK_REG 0x00000508 |

| #define PIC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define PIC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define PIC_CLK_REG_CLK_SRC_SEL_PERI_200M 0b0 |

| #define PIC_CLK_REG_CLK_SRC_SEL_PERI_400M 0b1 |

| #define PIC_CLK_REG_PIC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define PIC_CLK_REG_PIC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define PIC_CLK_REG_PIC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define PIC_CLK_REG_PIC_CLK_GATING_OFFSET 31 |

| #define PLL_AUDIO_BIAS_REG 0x00000378 |

| #define PLL_AUDIO_BIAS_REG_PLL_CP_CLEAR_MASK 0x001f0000 |

| #define PLL_AUDIO_BIAS_REG_PLL_CP_OFFSET 16 |

| #define PLL_AUDIO_CTRL_REG 0x00000078 |

| #define PLL_AUDIO_CTRL_REG_LOCK_CLEAR_MASK 0x10000000 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_CLEAR_MASK 0x20000000 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_OFFSET 29 |

| #define PLL_AUDIO_CTRL_REG_LOCK_LOCKED__IT_INDICATES_THAT_THE_PLL_HAS_BEEN_STABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_LOCK_OFFSET 28 |

| #define PLL_AUDIO_CTRL_REG_LOCK_UNLOCKED 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_CLEAR_MASK 0x80000000 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_OFFSET 31 |

| #define PLL_AUDIO_CTRL_REG_PLL_FACTOR_N_CLEAR_MASK 0x0000ff00 |

| #define PLL_AUDIO_CTRL_REG_PLL_FACTOR_N_OFFSET 8 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV2_CLEAR_MASK 0x00000002 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV2_OFFSET 1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_CLEAR_MASK 0x40000000 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_OFFSET 30 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_23_27_CLOCK_CYCLES 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_24_26_CLOCK_CYCLES 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_CLEAR_MASK 0x00000020 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_OFFSET 5 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_CLEAR_MASK 0x08000000 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_OFFSET 27 |

| #define PLL_AUDIO_CTRL_REG_PLL_P0_CLEAR_MASK 0x00070000 |

| #define PLL_AUDIO_CTRL_REG_PLL_P0_OFFSET 16 |

| #define PLL_AUDIO_CTRL_REG_PLL_P1_CLEAR_MASK 0x00700000 |

| #define PLL_AUDIO_CTRL_REG_PLL_P1_OFFSET 20 |

| #define PLL_AUDIO_CTRL_REG_PLL_P2_CLEAR_MASK 0x0000001c |

| #define PLL_AUDIO_CTRL_REG_PLL_P2_OFFSET 2 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_CLEAR_MASK 0x01000000 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_OFFSET 24 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_20_30_CLOCK_CYCLES 0b10 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_21_29_CLOCK_CYCLES 0b00 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_22_28_CLOCK_CYCLES 0b01 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_CLEAR_MASK 0x000000c0 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_OFFSET 6 |

| #define PLL_AUDIO_PAT0_CTRL_REG 0x00000178 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_31_5KHZ 0b00 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_32_5KHZ 0b10 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_32KHZ 0b01 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_33KHZ 0b11 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_CLEAR_MASK 0x00060000 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_OFFSET 17 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_12MHZ 0b1 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_24MHZ 0b0 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_CLEAR_MASK 0x00080000 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_OFFSET 19 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SIG_DELT_PAT_EN_CLEAR_MASK 0x80000000 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SIG_DELT_PAT_EN_OFFSET 31 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_CLEAR_MASK 0x60000000 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_0 0b00 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_1 0b01 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_OFFSET 29 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_1BIT 0b10 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_NBIT 0b11 |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_BOT_CLEAR_MASK 0x0001ffff |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_BOT_OFFSET 0 |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_STEP_CLEAR_MASK 0x1ff00000 |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_STEP_OFFSET 20 |