|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

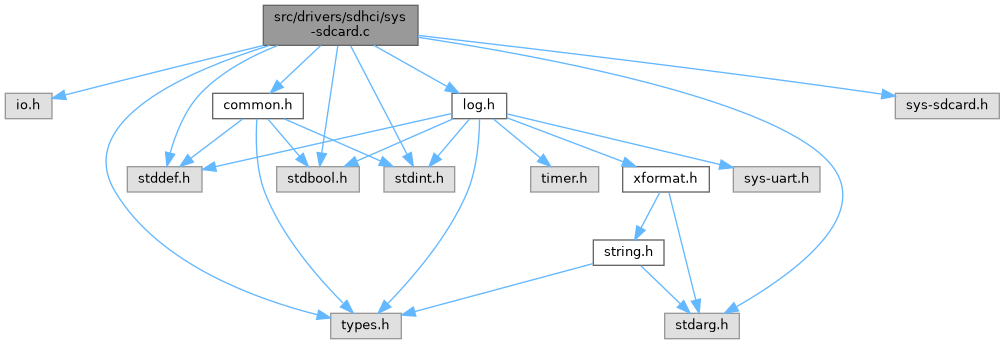

#include <io.h>#include <stdarg.h>#include <stdbool.h>#include <stddef.h>#include <stdint.h>#include <types.h>#include <log.h>#include <common.h>#include "sys-sdcard.h"

Macros | |

| #define | FALSE 0 |

| #define | TRUE 1 |

| #define | EXT_CSD_CMDQ_MODE_EN 15 /* R/W */ |

| #define | EXT_CSD_FLUSH_CACHE 32 /* W */ |

| #define | EXT_CSD_CACHE_CTRL 33 /* R/W */ |

| #define | EXT_CSD_POWER_OFF_NOTIFICATION 34 /* R/W */ |

| #define | EXT_CSD_PACKED_FAILURE_INDEX 35 /* RO */ |

| #define | EXT_CSD_PACKED_CMD_STATUS 36 /* RO */ |

| #define | EXT_CSD_EXP_EVENTS_STATUS 54 /* RO, 2 bytes */ |

| #define | EXT_CSD_EXP_EVENTS_CTRL 56 /* R/W, 2 bytes */ |

| #define | EXT_CSD_DATA_SECTOR_SIZE 61 /* R */ |

| #define | EXT_CSD_GP_SIZE_MULT 143 /* R/W */ |

| #define | EXT_CSD_PARTITION_SETTING_COMPLETED 155 /* R/W */ |

| #define | EXT_CSD_PARTITION_ATTRIBUTE 156 /* R/W */ |

| #define | EXT_CSD_PARTITION_SUPPORT 160 /* RO */ |

| #define | EXT_CSD_HPI_MGMT 161 /* R/W */ |

| #define | EXT_CSD_RST_N_FUNCTION 162 /* R/W */ |

| #define | EXT_CSD_BKOPS_EN 163 /* R/W */ |

| #define | EXT_CSD_BKOPS_START 164 /* W */ |

| #define | EXT_CSD_SANITIZE_START 165 /* W */ |

| #define | EXT_CSD_WR_REL_PARAM 166 /* RO */ |

| #define | EXT_CSD_RPMB_MULT 168 /* RO */ |

| #define | EXT_CSD_FW_CONFIG 169 /* R/W */ |

| #define | EXT_CSD_BOOT_WP 173 /* R/W */ |

| #define | EXT_CSD_ERASE_GROUP_DEF 175 /* R/W */ |

| #define | EXT_CSD_PART_CONFIG 179 /* R/W */ |

| #define | EXT_CSD_ERASED_MEM_CONT 181 /* RO */ |

| #define | EXT_CSD_BUS_WIDTH 183 /* R/W */ |

| #define | EXT_CSD_STROBE_SUPPORT 184 /* RO */ |

| #define | EXT_CSD_HS_TIMING 185 /* R/W */ |

| #define | EXT_CSD_POWER_CLASS 187 /* R/W */ |

| #define | EXT_CSD_REV 192 /* RO */ |

| #define | EXT_CSD_STRUCTURE 194 /* RO */ |

| #define | EXT_CSD_CARD_TYPE 196 /* RO */ |

| #define | EXT_CSD_DRIVER_STRENGTH 197 /* RO */ |

| #define | EXT_CSD_OUT_OF_INTERRUPT_TIME 198 /* RO */ |

| #define | EXT_CSD_PART_SWITCH_TIME 199 /* RO */ |

| #define | EXT_CSD_PWR_CL_52_195 200 /* RO */ |

| #define | EXT_CSD_PWR_CL_26_195 201 /* RO */ |

| #define | EXT_CSD_PWR_CL_52_360 202 /* RO */ |

| #define | EXT_CSD_PWR_CL_26_360 203 /* RO */ |

| #define | EXT_CSD_SEC_CNT 212 /* RO, 4 bytes */ |

| #define | EXT_CSD_S_A_TIMEOUT 217 /* RO */ |

| #define | EXT_CSD_REL_WR_SEC_C 222 /* RO */ |

| #define | EXT_CSD_HC_WP_GRP_SIZE 221 /* RO */ |

| #define | EXT_CSD_ERASE_TIMEOUT_MULT 223 /* RO */ |

| #define | EXT_CSD_HC_ERASE_GRP_SIZE 224 /* RO */ |

| #define | EXT_CSD_BOOT_MULT 226 /* RO */ |

| #define | EXT_CSD_SEC_TRIM_MULT 229 /* RO */ |

| #define | EXT_CSD_SEC_ERASE_MULT 230 /* RO */ |

| #define | EXT_CSD_SEC_FEATURE_SUPPORT 231 /* RO */ |

| #define | EXT_CSD_TRIM_MULT 232 /* RO */ |

| #define | EXT_CSD_PWR_CL_200_195 236 /* RO */ |

| #define | EXT_CSD_PWR_CL_200_360 237 /* RO */ |

| #define | EXT_CSD_PWR_CL_DDR_52_195 238 /* RO */ |

| #define | EXT_CSD_PWR_CL_DDR_52_360 239 /* RO */ |

| #define | EXT_CSD_BKOPS_STATUS 246 /* RO */ |

| #define | EXT_CSD_POWER_OFF_LONG_TIME 247 /* RO */ |

| #define | EXT_CSD_GENERIC_CMD6_TIME 248 /* RO */ |

| #define | EXT_CSD_CACHE_SIZE 249 /* RO, 4 bytes */ |

| #define | EXT_CSD_PWR_CL_DDR_200_360 253 /* RO */ |

| #define | EXT_CSD_FIRMWARE_VERSION 254 /* RO, 8 bytes */ |

| #define | EXT_CSD_PRE_EOL_INFO 267 /* RO */ |

| #define | EXT_CSD_DEVICE_LIFE_TIME_EST_TYP_A 268 /* RO */ |

| #define | EXT_CSD_DEVICE_LIFE_TIME_EST_TYP_B 269 /* RO */ |

| #define | EXT_CSD_CMDQ_DEPTH 307 /* RO */ |

| #define | EXT_CSD_CMDQ_SUPPORT 308 /* RO */ |

| #define | EXT_CSD_SUPPORTED_MODE 493 /* RO */ |

| #define | EXT_CSD_TAG_UNIT_SIZE 498 /* RO */ |

| #define | EXT_CSD_DATA_TAG_SUPPORT 499 /* RO */ |

| #define | EXT_CSD_MAX_PACKED_WRITES 500 /* RO */ |

| #define | EXT_CSD_MAX_PACKED_READS 501 /* RO */ |

| #define | EXT_CSD_BKOPS_SUPPORT 502 /* RO */ |

| #define | EXT_CSD_HPI_FEATURES 503 /* RO */ |

| #define | EXT_CSD_BUS_WIDTH_1 0 /* Card is in 1 bit mode */ |

| #define | EXT_CSD_BUS_WIDTH_4 1 /* Card is in 4 bit mode */ |

| #define | EXT_CSD_BUS_WIDTH_8 2 /* Card is in 8 bit mode */ |

| #define | EXT_CSD_DDR_BUS_WIDTH_4 5 /* Card is in 4 bit DDR mode */ |

| #define | EXT_CSD_DDR_BUS_WIDTH_8 6 /* Card is in 8 bit DDR mode */ |

| #define | EXT_CSD_CARD_TYPE_26 (1 << 0) /* Card can run at 26MHz */ |

| #define | EXT_CSD_CARD_TYPE_52 (1 << 1) /* Card can run at 52MHz */ |

| #define | EXT_CSD_CARD_TYPE_MASK 0x3F /* Mask out reserved bits */ |

| #define | EXT_CSD_CARD_TYPE_DDR_1_8V (1 << 2) /* Card can run at 52MHz */ |

| #define | EXT_CSD_CARD_TYPE_DDR_1_2V (1 << 3) /* Card can run at 52MHz */ |

| #define | EXT_CSD_CARD_TYPE_DDR_52 (EXT_CSD_CARD_TYPE_DDR_1_8V | EXT_CSD_CARD_TYPE_DDR_1_2V) |

| #define | EXT_CSD_CARD_TYPE_SDR_1_8V (1 << 4) /* Card can run at 200MHz */ |

| #define | EXT_CSD_CARD_TYPE_SDR_1_2V (1 << 5) /* Card can run at 200MHz */ |

| #define | EXT_CSD_CMD_SET_NORMAL (1 << 0) |

| #define | EXT_CSD_CMD_SET_SECURE (1 << 1) |

| #define | EXT_CSD_CMD_SET_CPSECURE (1 << 2) |

| #define | EXT_CSD_PWR_CL_8BIT_MASK 0xF0 /* 8 bit PWR CLS */ |

| #define | EXT_CSD_PWR_CL_4BIT_MASK 0x0F /* 8 bit PWR CLS */ |

| #define | EXT_CSD_PWR_CL_8BIT_SHIFT 4 |

| #define | EXT_CSD_PWR_CL_4BIT_SHIFT 0 |

| #define | UNSTUFF_BITS(resp, start, size) |

Variables | |

| sdmmc_pdata_t | card0 |

| External declaration of the 'card0' SDMMC platform data structure. | |

| static const unsigned | tran_speed_unit [] |

| static const unsigned char | tran_speed_time [] |

| #define EXT_CSD_BKOPS_EN 163 /* R/W */ |

| #define EXT_CSD_BKOPS_START 164 /* W */ |

| #define EXT_CSD_BKOPS_STATUS 246 /* RO */ |

| #define EXT_CSD_BKOPS_SUPPORT 502 /* RO */ |

| #define EXT_CSD_BOOT_MULT 226 /* RO */ |

| #define EXT_CSD_BOOT_WP 173 /* R/W */ |

| #define EXT_CSD_BUS_WIDTH 183 /* R/W */ |

| #define EXT_CSD_BUS_WIDTH_1 0 /* Card is in 1 bit mode */ |

| #define EXT_CSD_BUS_WIDTH_4 1 /* Card is in 4 bit mode */ |

| #define EXT_CSD_BUS_WIDTH_8 2 /* Card is in 8 bit mode */ |

| #define EXT_CSD_CACHE_CTRL 33 /* R/W */ |

| #define EXT_CSD_CACHE_SIZE 249 /* RO, 4 bytes */ |

| #define EXT_CSD_CARD_TYPE 196 /* RO */ |

| #define EXT_CSD_CARD_TYPE_26 (1 << 0) /* Card can run at 26MHz */ |

| #define EXT_CSD_CARD_TYPE_52 (1 << 1) /* Card can run at 52MHz */ |

| #define EXT_CSD_CARD_TYPE_DDR_1_2V (1 << 3) /* Card can run at 52MHz */ |

| #define EXT_CSD_CARD_TYPE_DDR_1_8V (1 << 2) /* Card can run at 52MHz */ |

| #define EXT_CSD_CARD_TYPE_DDR_52 (EXT_CSD_CARD_TYPE_DDR_1_8V | EXT_CSD_CARD_TYPE_DDR_1_2V) |

| #define EXT_CSD_CARD_TYPE_MASK 0x3F /* Mask out reserved bits */ |

| #define EXT_CSD_CARD_TYPE_SDR_1_2V (1 << 5) /* Card can run at 200MHz */ |

| #define EXT_CSD_CARD_TYPE_SDR_1_8V (1 << 4) /* Card can run at 200MHz */ |

| #define EXT_CSD_CMD_SET_CPSECURE (1 << 2) |

| #define EXT_CSD_CMD_SET_NORMAL (1 << 0) |

| #define EXT_CSD_CMD_SET_SECURE (1 << 1) |

| #define EXT_CSD_CMDQ_DEPTH 307 /* RO */ |

| #define EXT_CSD_CMDQ_MODE_EN 15 /* R/W */ |

| #define EXT_CSD_CMDQ_SUPPORT 308 /* RO */ |

| #define EXT_CSD_DATA_SECTOR_SIZE 61 /* R */ |

| #define EXT_CSD_DATA_TAG_SUPPORT 499 /* RO */ |

| #define EXT_CSD_DDR_BUS_WIDTH_4 5 /* Card is in 4 bit DDR mode */ |

| #define EXT_CSD_DDR_BUS_WIDTH_8 6 /* Card is in 8 bit DDR mode */ |

| #define EXT_CSD_DEVICE_LIFE_TIME_EST_TYP_A 268 /* RO */ |

| #define EXT_CSD_DEVICE_LIFE_TIME_EST_TYP_B 269 /* RO */ |

| #define EXT_CSD_DRIVER_STRENGTH 197 /* RO */ |

| #define EXT_CSD_ERASE_GROUP_DEF 175 /* R/W */ |

| #define EXT_CSD_ERASE_TIMEOUT_MULT 223 /* RO */ |

| #define EXT_CSD_ERASED_MEM_CONT 181 /* RO */ |

| #define EXT_CSD_EXP_EVENTS_CTRL 56 /* R/W, 2 bytes */ |

| #define EXT_CSD_EXP_EVENTS_STATUS 54 /* RO, 2 bytes */ |

| #define EXT_CSD_FIRMWARE_VERSION 254 /* RO, 8 bytes */ |

| #define EXT_CSD_FLUSH_CACHE 32 /* W */ |

| #define EXT_CSD_FW_CONFIG 169 /* R/W */ |

| #define EXT_CSD_GENERIC_CMD6_TIME 248 /* RO */ |

| #define EXT_CSD_GP_SIZE_MULT 143 /* R/W */ |

| #define EXT_CSD_HC_ERASE_GRP_SIZE 224 /* RO */ |

| #define EXT_CSD_HC_WP_GRP_SIZE 221 /* RO */ |

| #define EXT_CSD_HPI_FEATURES 503 /* RO */ |

| #define EXT_CSD_HPI_MGMT 161 /* R/W */ |

| #define EXT_CSD_HS_TIMING 185 /* R/W */ |

| #define EXT_CSD_MAX_PACKED_READS 501 /* RO */ |

| #define EXT_CSD_MAX_PACKED_WRITES 500 /* RO */ |

| #define EXT_CSD_OUT_OF_INTERRUPT_TIME 198 /* RO */ |

| #define EXT_CSD_PACKED_CMD_STATUS 36 /* RO */ |

| #define EXT_CSD_PACKED_FAILURE_INDEX 35 /* RO */ |

| #define EXT_CSD_PART_CONFIG 179 /* R/W */ |

| #define EXT_CSD_PART_SWITCH_TIME 199 /* RO */ |

| #define EXT_CSD_PARTITION_ATTRIBUTE 156 /* R/W */ |

| #define EXT_CSD_PARTITION_SETTING_COMPLETED 155 /* R/W */ |

| #define EXT_CSD_PARTITION_SUPPORT 160 /* RO */ |

| #define EXT_CSD_POWER_CLASS 187 /* R/W */ |

| #define EXT_CSD_POWER_OFF_LONG_TIME 247 /* RO */ |

| #define EXT_CSD_POWER_OFF_NOTIFICATION 34 /* R/W */ |

| #define EXT_CSD_PRE_EOL_INFO 267 /* RO */ |

| #define EXT_CSD_PWR_CL_200_195 236 /* RO */ |

| #define EXT_CSD_PWR_CL_200_360 237 /* RO */ |

| #define EXT_CSD_PWR_CL_26_195 201 /* RO */ |

| #define EXT_CSD_PWR_CL_26_360 203 /* RO */ |

| #define EXT_CSD_PWR_CL_4BIT_MASK 0x0F /* 8 bit PWR CLS */ |

| #define EXT_CSD_PWR_CL_4BIT_SHIFT 0 |

| #define EXT_CSD_PWR_CL_52_195 200 /* RO */ |

| #define EXT_CSD_PWR_CL_52_360 202 /* RO */ |

| #define EXT_CSD_PWR_CL_8BIT_MASK 0xF0 /* 8 bit PWR CLS */ |

| #define EXT_CSD_PWR_CL_8BIT_SHIFT 4 |

| #define EXT_CSD_PWR_CL_DDR_200_360 253 /* RO */ |

| #define EXT_CSD_PWR_CL_DDR_52_195 238 /* RO */ |

| #define EXT_CSD_PWR_CL_DDR_52_360 239 /* RO */ |

| #define EXT_CSD_REL_WR_SEC_C 222 /* RO */ |

| #define EXT_CSD_REV 192 /* RO */ |

| #define EXT_CSD_RPMB_MULT 168 /* RO */ |

| #define EXT_CSD_RST_N_FUNCTION 162 /* R/W */ |

| #define EXT_CSD_S_A_TIMEOUT 217 /* RO */ |

| #define EXT_CSD_SANITIZE_START 165 /* W */ |

| #define EXT_CSD_SEC_CNT 212 /* RO, 4 bytes */ |

| #define EXT_CSD_SEC_ERASE_MULT 230 /* RO */ |

| #define EXT_CSD_SEC_FEATURE_SUPPORT 231 /* RO */ |

| #define EXT_CSD_SEC_TRIM_MULT 229 /* RO */ |

| #define EXT_CSD_STROBE_SUPPORT 184 /* RO */ |

| #define EXT_CSD_STRUCTURE 194 /* RO */ |

| #define EXT_CSD_SUPPORTED_MODE 493 /* RO */ |

| #define EXT_CSD_TAG_UNIT_SIZE 498 /* RO */ |

| #define EXT_CSD_TRIM_MULT 232 /* RO */ |

| #define EXT_CSD_WR_REL_PARAM 166 /* RO */ |

| #define FALSE 0 |

| #define TRUE 1 |

| #define UNSTUFF_BITS | ( | resp, | |

| start, | |||

| size | |||

| ) |

| uint64_t sdmmc_blk_read | ( | sdmmc_pdata_t * | data, |

| uint8_t * | buf, | ||

| uint64_t | blkno, | ||

| uint64_t | blkcnt | ||

| ) |

Read data from the SDMMC card into the provided buffer.

| data | Pointer to the SDMMC platform data structure. |

| buf | Pointer to the destination buffer to store the read data. |

| blkno | The starting block number to read from. |

| blkcnt | The number of blocks to read. |

| uint64_t sdmmc_blk_write | ( | sdmmc_pdata_t * | data, |

| uint8_t * | buf, | ||

| uint64_t | blkno, | ||

| uint64_t | blkcnt | ||

| ) |

| int sdmmc_init | ( | sdmmc_pdata_t * | data, |

| sdhci_t * | hci | ||

| ) |

Initialize the SDMMC controller with the specified platform data and SDHCI driver.

| data | Pointer to the SDMMC platform data structure. |

| hci | Pointer to the SDHCI driver instance. |

|

static |

|

static |

| sdmmc_pdata_t card0 |

External declaration of the 'card0' SDMMC platform data structure.

|

static |

|

static |