|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

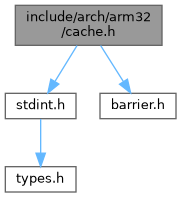

Cache control functions for ARM32 architecture. More...

Go to the source code of this file.

Functions | |

| static void | arm32_dcache_enable (void) |

| Enable the ARM32 data cache. | |

| static void | arm32_dcache_disable (void) |

| Disable the ARM32 data cache. | |

| static void | arm32_icache_enable (void) |

| Enable the ARM32 instruction cache. | |

| static void | arm32_icache_disable (void) |

| Disable the ARM32 instruction cache. | |

| static void | flush_dcache_range (uint64_t start, uint64_t end) |

| Flush a range of addresses from the data cache. | |

| static void | invalidate_dcache_range (uint64_t start, uint64_t end) |

| Invalidate a range of addresses in the data cache. | |

| static void | flush_dcache_all () |

| Flush (clean) the entire data cache. | |

| static void | invalidate_dcache_all () |

| Invalidate the entire data cache. | |

| static void | data_sync_barrier (void) |

| Insert a data synchronization barrier. | |

Cache control functions for ARM32 architecture.

This header file provides functions for controlling data and instruction caches on ARM32 architecture.

|

inlinestatic |

Disable the ARM32 data cache.

This function disables the data cache by clearing the C-bit in the system control register.

|

inlinestatic |

Enable the ARM32 data cache.

This function enables the data cache by setting the C-bit in the system control register.

|

inlinestatic |

Disable the ARM32 instruction cache.

This function disables the instruction cache by clearing the I-bit in the system control register.

|

inlinestatic |

Enable the ARM32 instruction cache.

This function enables the instruction cache by setting the I-bit in the system control register.

|

inlinestatic |

Insert a data synchronization barrier.

This function ensures that all previous instructions are completed before any subsequent instructions are executed, particularly useful for ensuring memory consistency.

|

inlinestatic |

Flush (clean) the entire data cache.

This function flushes all data cache lines, ensuring that any modified data is written back to memory. It uses a single CP15 instruction to clean the entire cache.

Flush a range of addresses from the data cache.

This function flushes (cleans) a specified range of addresses from the data cache, ensuring that any modified data is written back to memory. The function aligns the addresses to cache line boundaries and processes each line individually.

| start | The starting address of the range to flush. |

| end | The ending address of the range to flush (inclusive). |

|

inlinestatic |

Invalidate the entire data cache.

This function invalidates all data cache lines, discarding any data they contain. Subsequent reads will fetch fresh data from memory. It uses a single CP15 instruction to invalidate the entire cache.

Invalidate a range of addresses in the data cache.

This function invalidates a specified range of addresses in the data cache, ensuring that subsequent reads will fetch fresh data from memory rather than using potentially stale cached data. The function aligns the addresses to cache line boundaries and processes each line individually.

| start | The starting address of the range to invalidate. |

| end | The ending address of the range to invalidate (inclusive). |