|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

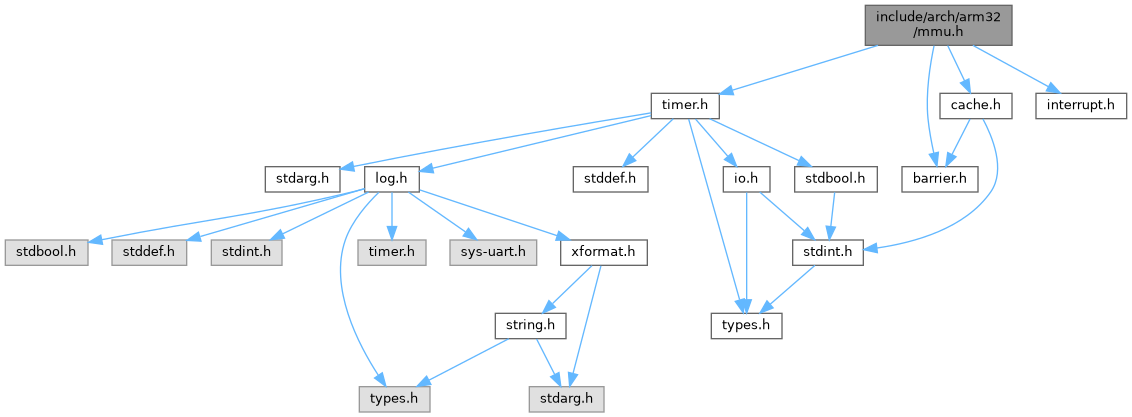

Memory Management Unit (MMU) interface for ARM32 architecture. More...

Go to the source code of this file.

Classes | |

| struct | arm_regs_t |

| ARM32 register structure. More... | |

Functions | |

| static uint32_t | arm32_read_p15_c1 (void) |

| Read the ARM32 system control register (CP15, c1). | |

| static void | arm32_write_p15_c1 (uint32_t value) |

| Write to the ARM32 system control register (CP15, c1). | |

| static void | arm32_mmu_enable (const uint32_t dram_base, uint32_t dram_size) |

| Enable the ARM32 MMU with specific memory configuration. | |

| static void | arm32_mmu_disable (void) |

| Disable the ARM32 MMU and clear caches. | |

Memory Management Unit (MMU) interface for ARM32 architecture.

This header file provides functions and definitions for managing the Memory Management Unit on ARM32 architecture. It includes functions for enabling/disabling MMU and MMU control operations.

|

inlinestatic |

Disable the ARM32 MMU and clear caches.

This function disables the Memory Management Unit (MMU), instruction cache, and data cache. It also invalidates the instruction cache, branch predictor, and ensures all operations are completed with memory barriers.

Enable the ARM32 MMU with specific memory configuration.

This function initializes and enables the Memory Management Unit (MMU) for ARM32 architecture. It sets up page tables with appropriate memory attributes and configures the MMU control registers.

| dram_base | Base address of DRAM memory. |

| dram_size | Size of DRAM memory in megabytes. |

|

inlinestatic |

Read the ARM32 system control register (CP15, c1).

This function reads the value of the ARM32 system control register (CP15, c1), which controls various system features including MMU, caches, and alignment checking.

|

inlinestatic |

Write to the ARM32 system control register (CP15, c1).

This function writes a value to the ARM32 system control register (CP15, c1), which controls various system features including MMU, caches, and alignment checking. A read-back is performed to ensure the write is completed.

| value | The value to write to the system control register. |