|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

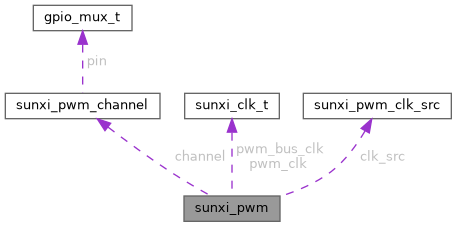

Main PWM configuration structure. More...

#include <sys-pwm.h>

Public Attributes | |

| uint32_t | base |

| The base address of the PWM hardware module. | |

| uint8_t | id |

| The PWM module ID. | |

| sunxi_pwm_channel_t * | channel |

| Pointer to the array of PWM channels. | |

| uint32_t | channel_size |

| The number of PWM channels. | |

| sunxi_clk_t | pwm_bus_clk |

| Clock for the PWM bus. | |

| sunxi_clk_t | pwm_clk |

| The main clock for the PWM module. | |

| sunxi_pwm_clk_src_t | clk_src |

| The clock sources for the PWM module. | |

| bool | status |

| The operational status of the PWM module (enabled/disabled). | |

Main PWM configuration structure.

This structure holds the complete configuration for the PWM module, including the base address, channel settings, clock source settings, and the module's operational status.

| uint32_t sunxi_pwm::base |

The base address of the PWM hardware module.

| sunxi_pwm_channel_t* sunxi_pwm::channel |

Pointer to the array of PWM channels.

| uint32_t sunxi_pwm::channel_size |

The number of PWM channels.

| sunxi_pwm_clk_src_t sunxi_pwm::clk_src |

The clock sources for the PWM module.

| uint8_t sunxi_pwm::id |

The PWM module ID.

| sunxi_clk_t sunxi_pwm::pwm_bus_clk |

Clock for the PWM bus.

| sunxi_clk_t sunxi_pwm::pwm_clk |

The main clock for the PWM module.

| bool sunxi_pwm::status |

The operational status of the PWM module (enabled/disabled).