|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

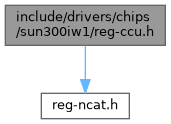

#include <reg-ncat.h>

Go to the source code of this file.

| #define A27L2_CLK_REG 0x00000588 |

| #define A27L2_CLK_REG_A27L2_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define A27L2_CLK_REG_A27L2_CLK_DIV_OFFSET 0 |

| #define A27L2_CLK_REG_A27L2_CLK_EN_CLEAR_MASK (0x80000000) |

| #define A27L2_CLK_REG_A27L2_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define A27L2_CLK_REG_A27L2_CLK_EN_CLOCK_IS_ON 0b1 |

| #define A27L2_CLK_REG_A27L2_CLK_EN_OFFSET 31 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_CPU_PLL 0b100 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_HOSC 0b000 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_OFFSET 24 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_PERI_PLL_1024M 0b101 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_PERI_PLL_768M 0b110 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_PERI_PLL_768M0 0b111 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_RC1M 0b010 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_RC1M0 0b011 |

| #define A27L2_CLK_REG_A27L2_CLK_SEL_VIDEOPLL2X 0b001 |

| #define A27L2_MT_CLK_EN_CLEAR_MASK (0x80000000) |

| #define A27L2_MT_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define A27L2_MT_CLK_EN_CLOCK_IS_ON 0b1 |

| #define A27L2_MT_CLK_SEL_CLEAR_MASK (0x01000000) |

| #define A27L2_MT_CLK_SEL_HOSC 0b0 |

| #define A27L2_MT_CLK_SEL_OFFSET 24 |

| #define A27L2_MT_CLK_SEL_SYS_32K 0b1 |

| #define A27L2_MT_Clock_REG 0x00000010 |

| #define AHB_CLK_REG 0x00000500 |

| #define AHB_CLK_REG_AHB_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define AHB_CLK_REG_AHB_CLK_DIV_OFFSET 0 |

| #define AHB_CLK_REG_AHB_SEL_CLEAR_MASK (0x03000000) |

| #define AHB_CLK_REG_AHB_SEL_HOSC 0b00 |

| #define AHB_CLK_REG_AHB_SEL_OFFSET 24 |

| #define AHB_CLK_REG_AHB_SEL_PERI_768M 0b01 |

| #define AHB_CLK_REG_AHB_SEL_RC1M 0b10 |

| #define AHB_CLK_REG_AHB_SEL_SYS32K_NO_USE 0b11 |

| #define APB_CLK_REG 0x00000504 |

| #define APB_CLK_REG_APB_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define APB_CLK_REG_APB_CLK_DIV_OFFSET 0 |

| #define APB_CLK_REG_APB_SEL_CLEAR_MASK (0x03000000) |

| #define APB_CLK_REG_APB_SEL_HOSC 0b00 |

| #define APB_CLK_REG_APB_SEL_OFFSET 24 |

| #define APB_CLK_REG_APB_SEL_PERI_384M 0b01 |

| #define APB_CLK_REG_APB_SEL_RC1M 0b10 |

| #define APB_CLK_REG_APB_SEL_SYS32K_NO_USE 0b11 |

| #define APB_SPEC_CLK_REG 0x00000580 |

| #define APB_SPEC_CLK_REG_APB_SPEC_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define APB_SPEC_CLK_REG_APB_SPEC_CLK_DIV_OFFSET 0 |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_CLEAR_MASK (0x03000000) |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_HOSC 0b00 |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_OFFSET 24 |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_PERI_192M 0b11 |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_RC1M 0b10 |

| #define APB_SPEC_CLK_REG_APB_SPEC_SEL_SYS32K_NO_USE 0b01 |

| #define AUDIO_DIV_CLK_REG 0x00000060 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_DIV_CLEAR_MASK (0x0000001f) |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_DIV_OFFSET 0 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_SEL_CLEAR_MASK (0x03000000) |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_SEL_CPUPLL 0b01 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_SEL_OFFSET 24 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_SEL_PERI_614M 0b00 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL1X_SEL_VIDEOPLL2X 0b10 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_DIV_CLEAR_MASK (0x000003e0) |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_DIV_OFFSET 5 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_SEL_CLEAR_MASK (0x0c000000) |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_SEL_CPUPLL 0b01 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_SEL_OFFSET 26 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_SEL_PERI_1536M 0b00 |

| #define AUDIO_DIV_CLK_REG_AUDIOPLL4X_SEL_VIDEOPLL2X 0b10 |

| #define BUS_CLK_GATING0_REG 0x00000080 |

| #define BUS_CLK_GATING0_REG_CE_HCLK_EN_CLEAR_MASK (0x00000040) |

| #define BUS_CLK_GATING0_REG_CE_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_CE_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_CE_HCLK_EN_OFFSET 6 |

| #define BUS_CLK_GATING0_REG_DMA_HCLK_EN_CLEAR_MASK (0x00000100) |

| #define BUS_CLK_GATING0_REG_DMA_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_DMA_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_DMA_HCLK_EN_OFFSET 8 |

| #define BUS_CLK_GATING0_REG_DPSS_TOP_CLK_EN_CLEAR_MASK (0x80000000) |

| #define BUS_CLK_GATING0_REG_DPSS_TOP_CLK_EN_MASK 0b0 |

| #define BUS_CLK_GATING0_REG_DPSS_TOP_CLK_EN_OFFSET 31 |

| #define BUS_CLK_GATING0_REG_DPSS_TOP_CLK_EN_PASS 0b1 |

| #define BUS_CLK_GATING0_REG_DRAM_GATING_CLEAR_MASK (0x00000008) |

| #define BUS_CLK_GATING0_REG_DRAM_GATING_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_DRAM_GATING_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_DRAM_GATING_OFFSET 3 |

| #define BUS_CLK_GATING0_REG_GMAC_HCLK_EN_CLEAR_MASK (0x01000000) |

| #define BUS_CLK_GATING0_REG_GMAC_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_GMAC_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_GMAC_HCLK_EN_OFFSET 24 |

| #define BUS_CLK_GATING0_REG_GPIO_PCLK_EN_CLEAR_MASK (0x40000000) |

| #define BUS_CLK_GATING0_REG_GPIO_PCLK_EN_MASK 0b0 |

| #define BUS_CLK_GATING0_REG_GPIO_PCLK_EN_OFFSET 30 |

| #define BUS_CLK_GATING0_REG_GPIO_PCLK_EN_PASS 0b1 |

| #define BUS_CLK_GATING0_REG_HSTIMER_HCLKEN_CLEAR_MASK (0x00000020) |

| #define BUS_CLK_GATING0_REG_HSTIMER_HCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_HSTIMER_HCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_HSTIMER_HCLKEN_OFFSET 5 |

| #define BUS_CLK_GATING0_REG_MCSI_AHB_CLK_EN_CLEAR_MASK (0x10000000) |

| #define BUS_CLK_GATING0_REG_MCSI_AHB_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_MCSI_AHB_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_MCSI_AHB_CLK_EN_OFFSET 28 |

| #define BUS_CLK_GATING0_REG_MCSI_MBUS_CLK_EN_CLEAR_MASK (0x08000000) |

| #define BUS_CLK_GATING0_REG_MCSI_MBUS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_MCSI_MBUS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_MCSI_MBUS_CLK_EN_OFFSET 27 |

| #define BUS_CLK_GATING0_REG_PWM_PCLK_EN_CLEAR_MASK (0x00002000) |

| #define BUS_CLK_GATING0_REG_PWM_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_PWM_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_PWM_PCLK_EN_OFFSET 13 |

| #define BUS_CLK_GATING0_REG_RISCV_CFG_CLKEN_CLEAR_MASK (0x00000001) |

| #define BUS_CLK_GATING0_REG_RISCV_CFG_CLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_RISCV_CFG_CLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_RISCV_CFG_CLKEN_OFFSET 0 |

| #define BUS_CLK_GATING0_REG_RV_MSGBOX_HCLKEN_CLEAR_MASK (0x00000004) |

| #define BUS_CLK_GATING0_REG_RV_MSGBOX_HCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_RV_MSGBOX_HCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_RV_MSGBOX_HCLKEN_OFFSET 2 |

| #define BUS_CLK_GATING0_REG_SGDMA_HCLK_EN_CLEAR_MASK (0x00000200) |

| #define BUS_CLK_GATING0_REG_SGDMA_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_SGDMA_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_SGDMA_HCLK_EN_OFFSET 9 |

| #define BUS_CLK_GATING0_REG_SPLOCK_HCLKEN_CLEAR_MASK (0x00000010) |

| #define BUS_CLK_GATING0_REG_SPLOCK_HCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_SPLOCK_HCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_SPLOCK_HCLKEN_OFFSET 4 |

| #define BUS_CLK_GATING0_REG_SYSCTRL_HCLK_EN_CLEAR_MASK (0x00000080) |

| #define BUS_CLK_GATING0_REG_SYSCTRL_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_SYSCTRL_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_SYSCTRL_HCLK_EN_OFFSET 7 |

| #define BUS_CLK_GATING0_REG_TIMER_PCLK_EN_CLEAR_MASK (0x00000400) |

| #define BUS_CLK_GATING0_REG_TIMER_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_TIMER_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_TIMER_PCLK_EN_OFFSET 10 |

| #define BUS_CLK_GATING0_REG_TRNG_PCLK_EN_CLEAR_MASK (0x00000800) |

| #define BUS_CLK_GATING0_REG_TRNG_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_TRNG_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_TRNG_PCLK_EN_OFFSET 11 |

| #define BUS_CLK_GATING0_REG_TWI0_PCLK_EN_CLEAR_MASK (0x00004000) |

| #define BUS_CLK_GATING0_REG_TWI0_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_TWI0_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_TWI0_PCLK_EN_OFFSET 14 |

| #define BUS_CLK_GATING0_REG_UART0_PCLK_EN_CLEAR_MASK (0x00008000) |

| #define BUS_CLK_GATING0_REG_UART0_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_UART0_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_UART0_PCLK_EN_OFFSET 15 |

| #define BUS_CLK_GATING0_REG_UART1_PCLK_EN_CLEAR_MASK (0x00010000) |

| #define BUS_CLK_GATING0_REG_UART1_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_UART1_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_UART1_PCLK_EN_OFFSET 16 |

| #define BUS_CLK_GATING0_REG_UART2_PCLK_EN_CLEAR_MASK (0x00020000) |

| #define BUS_CLK_GATING0_REG_UART2_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_UART2_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_UART2_PCLK_EN_OFFSET 17 |

| #define BUS_CLK_GATING0_REG_UART3_PCLK_EN_CLEAR_MASK (0x00040000) |

| #define BUS_CLK_GATING0_REG_UART3_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_UART3_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_UART3_PCLK_EN_OFFSET 18 |

| #define BUS_CLK_GATING0_REG_USB_HCLK_EN_CLEAR_MASK (0x00080000) |

| #define BUS_CLK_GATING0_REG_USB_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_USB_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_USB_HCLK_EN_OFFSET 19 |

| #define BUS_CLK_GATING0_REG_USBEHCI_BUSCLKEN_CLEAR_MASK (0x00200000) |

| #define BUS_CLK_GATING0_REG_USBEHCI_BUSCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_USBEHCI_BUSCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_USBEHCI_BUSCLKEN_OFFSET 21 |

| #define BUS_CLK_GATING0_REG_USBOHCI_BUSCLKEN_CLEAR_MASK (0x00400000) |

| #define BUS_CLK_GATING0_REG_USBOHCI_BUSCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_USBOHCI_BUSCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_USBOHCI_BUSCLKEN_OFFSET 22 |

| #define BUS_CLK_GATING0_REG_USBOTG_BUSCLKEN_CLEAR_MASK (0x00100000) |

| #define BUS_CLK_GATING0_REG_USBOTG_BUSCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_USBOTG_BUSCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_USBOTG_BUSCLKEN_OFFSET 20 |

| #define BUS_CLK_GATING0_REG_VID_OUT_AHB_CLK_EN_CLEAR_MASK (0x04000000) |

| #define BUS_CLK_GATING0_REG_VID_OUT_AHB_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_VID_OUT_AHB_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_VID_OUT_AHB_CLK_EN_OFFSET 26 |

| #define BUS_CLK_GATING0_REG_VID_OUT_MBUS_CLK_EN_CLEAR_MASK (0x02000000) |

| #define BUS_CLK_GATING0_REG_VID_OUT_MBUS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_VID_OUT_MBUS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_VID_OUT_MBUS_CLK_EN_OFFSET 25 |

| #define BUS_CLK_GATING0_REG_WG_PCLK_EN_CLEAR_MASK (0x00001000) |

| #define BUS_CLK_GATING0_REG_WG_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING0_REG_WG_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING0_REG_WG_PCLK_EN_OFFSET 12 |

| #define BUS_CLK_GATING0_REG_WKT_PCLK_EN_CLEAR_MASK (0x20000000) |

| #define BUS_CLK_GATING0_REG_WKT_PCLK_EN_MASK 0b0 |

| #define BUS_CLK_GATING0_REG_WKT_PCLK_EN_OFFSET 29 |

| #define BUS_CLK_GATING0_REG_WKT_PCLK_EN_PASS 0b1 |

| #define BUS_CLK_GATING1_REG 0x00000084 |

| #define BUS_CLK_GATING1_REG_ADDA_PCLK_EN_CLEAR_MASK (0x00000040) |

| #define BUS_CLK_GATING1_REG_ADDA_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_ADDA_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_ADDA_PCLK_EN_OFFSET 6 |

| #define BUS_CLK_GATING1_REG_DBGSYS_BUSCLKEN_CLEAR_MASK (0x00040000) |

| #define BUS_CLK_GATING1_REG_DBGSYS_BUSCLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_DBGSYS_BUSCLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_DBGSYS_BUSCLKEN_OFFSET 18 |

| #define BUS_CLK_GATING1_REG_DMA_MBUS_GATE_SW_CLEAR_MASK (0x00002000) |

| #define BUS_CLK_GATING1_REG_DMA_MBUS_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_DMA_MBUS_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_DMA_MBUS_GATE_SW_OFFSET 13 |

| #define BUS_CLK_GATING1_REG_DMIC_PCLK_EN_CLEAR_MASK (0x00000080) |

| #define BUS_CLK_GATING1_REG_DMIC_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_DMIC_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_DMIC_PCLK_EN_OFFSET 7 |

| #define BUS_CLK_GATING1_REG_G2D_CLK_EN_CLEAR_MASK (0x40000000) |

| #define BUS_CLK_GATING1_REG_G2D_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_G2D_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_G2D_CLK_EN_OFFSET 30 |

| #define BUS_CLK_GATING1_REG_G2D_HB_CLK_EN_CLEAR_MASK (0x20000000) |

| #define BUS_CLK_GATING1_REG_G2D_HB_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_G2D_HB_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_G2D_HB_CLK_EN_OFFSET 29 |

| #define BUS_CLK_GATING1_REG_G2D_MBUS_CLK_EN_CLEAR_MASK (0x80000000) |

| #define BUS_CLK_GATING1_REG_G2D_MBUS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_G2D_MBUS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_G2D_MBUS_CLK_EN_OFFSET 31 |

| #define BUS_CLK_GATING1_REG_GMAC_HBUS_EN_CLEAR_MASK (0x00400000) |

| #define BUS_CLK_GATING1_REG_GMAC_HBUS_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_GMAC_HBUS_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_GMAC_HBUS_EN_OFFSET 22 |

| #define BUS_CLK_GATING1_REG_GMAC_MBUS_AHB_GATE_SW_CLEAR_MASK (0x00020000) |

| #define BUS_CLK_GATING1_REG_GMAC_MBUS_AHB_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_GMAC_MBUS_AHB_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_GMAC_MBUS_AHB_GATE_SW_OFFSET 17 |

| #define BUS_CLK_GATING1_REG_GPA_PCLK_GATING_CLEAR_MASK (0x00000001) |

| #define BUS_CLK_GATING1_REG_GPA_PCLK_GATING_MASK 0b0 |

| #define BUS_CLK_GATING1_REG_GPA_PCLK_GATING_OFFSET 0 |

| #define BUS_CLK_GATING1_REG_GPA_PCLK_GATING_PASS 0b1 |

| #define BUS_CLK_GATING1_REG_I2S0_PCLK_EN_CLEAR_MASK (0x00000100) |

| #define BUS_CLK_GATING1_REG_I2S0_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_I2S0_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_I2S0_PCLK_EN_OFFSET 8 |

| #define BUS_CLK_GATING1_REG_I2S1_PCLK_EN_CLEAR_MASK (0x00000200) |

| #define BUS_CLK_GATING1_REG_I2S1_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_I2S1_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_I2S1_PCLK_EN_OFFSET 9 |

| #define BUS_CLK_GATING1_REG_MBUS_GATE_SW_CLEAR_MASK (0x00001000) |

| #define BUS_CLK_GATING1_REG_MBUS_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_MBUS_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_MBUS_GATE_SW_OFFSET 12 |

| #define BUS_CLK_GATING1_REG_MCSI_HCLK_EN_CLEAR_MASK (0x10000000) |

| #define BUS_CLK_GATING1_REG_MCSI_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_MCSI_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_MCSI_HCLK_EN_OFFSET 28 |

| #define BUS_CLK_GATING1_REG_MCSI_SCLK_EN_CLEAR_MASK (0x08000000) |

| #define BUS_CLK_GATING1_REG_MCSI_SCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_MCSI_SCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_MCSI_SCLK_EN_OFFSET 27 |

| #define BUS_CLK_GATING1_REG_MISP_SCLK_EN_CLEAR_MASK (0x04000000) |

| #define BUS_CLK_GATING1_REG_MISP_SCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_MISP_SCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_MISP_SCLK_EN_OFFSET 26 |

| #define BUS_CLK_GATING1_REG_SMHC0_HCLK_EN_CLEAR_MASK (0x00100000) |

| #define BUS_CLK_GATING1_REG_SMHC0_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SMHC0_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SMHC0_HCLK_EN_OFFSET 20 |

| #define BUS_CLK_GATING1_REG_SMHC0_MBUS_AHB_GATE_SW_CLEAR_MASK (0x00008000) |

| #define BUS_CLK_GATING1_REG_SMHC0_MBUS_AHB_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SMHC0_MBUS_AHB_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SMHC0_MBUS_AHB_GATE_SW_OFFSET 15 |

| #define BUS_CLK_GATING1_REG_SMHC1_HCLK_EN_CLEAR_MASK (0x00200000) |

| #define BUS_CLK_GATING1_REG_SMHC1_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SMHC1_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SMHC1_HCLK_EN_OFFSET 21 |

| #define BUS_CLK_GATING1_REG_SMHC1_MBUS_AHB_GATE_SW_CLEAR_MASK (0x00010000) |

| #define BUS_CLK_GATING1_REG_SMHC1_MBUS_AHB_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SMHC1_MBUS_AHB_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SMHC1_MBUS_AHB_GATE_SW_OFFSET 16 |

| #define BUS_CLK_GATING1_REG_SPI1_HCLK_EN_CLEAR_MASK (0x00080000) |

| #define BUS_CLK_GATING1_REG_SPI1_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SPI1_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SPI1_HCLK_EN_OFFSET 19 |

| #define BUS_CLK_GATING1_REG_SPI2_HCLK_EN_CLEAR_MASK (0x00800000) |

| #define BUS_CLK_GATING1_REG_SPI2_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SPI2_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SPI2_HCLK_EN_OFFSET 23 |

| #define BUS_CLK_GATING1_REG_SPI_HCLK_EN_CLEAR_MASK (0x00000010) |

| #define BUS_CLK_GATING1_REG_SPI_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SPI_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SPI_HCLK_EN_OFFSET 4 |

| #define BUS_CLK_GATING1_REG_SPIF_HCLK_EN_CLEAR_MASK (0x00000020) |

| #define BUS_CLK_GATING1_REG_SPIF_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_SPIF_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_SPIF_HCLK_EN_OFFSET 5 |

| #define BUS_CLK_GATING1_REG_THS_PCLK_GATING_CLEAR_MASK (0x00000002) |

| #define BUS_CLK_GATING1_REG_THS_PCLK_GATING_MASK 0b0 |

| #define BUS_CLK_GATING1_REG_THS_PCLK_GATING_OFFSET 1 |

| #define BUS_CLK_GATING1_REG_THS_PCLK_GATING_PASS 0b1 |

| #define BUS_CLK_GATING1_REG_TWI1_PCLK_EN_CLEAR_MASK (0x01000000) |

| #define BUS_CLK_GATING1_REG_TWI1_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_TWI1_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_TWI1_PCLK_EN_OFFSET 24 |

| #define BUS_CLK_GATING1_REG_TWI2_PCLK_EN_CLEAR_MASK (0x02000000) |

| #define BUS_CLK_GATING1_REG_TWI2_PCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_TWI2_PCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_TWI2_PCLK_EN_OFFSET 25 |

| #define BUS_CLK_GATING1_REG_USB_MBUS_AHB_GATE_SW_CLEAR_MASK (0x00004000) |

| #define BUS_CLK_GATING1_REG_USB_MBUS_AHB_GATE_SW_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_USB_MBUS_AHB_GATE_SW_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_USB_MBUS_AHB_GATE_SW_OFFSET 14 |

| #define BUS_CLK_GATING1_REG_VE_AHB_CLK_EN_CLEAR_MASK (0x00000008) |

| #define BUS_CLK_GATING1_REG_VE_AHB_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_VE_AHB_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_VE_AHB_CLK_EN_OFFSET 3 |

| #define BUS_CLK_GATING1_REG_VE_MBUS_CLK_EN_CLEAR_MASK (0x00000004) |

| #define BUS_CLK_GATING1_REG_VE_MBUS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING1_REG_VE_MBUS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING1_REG_VE_MBUS_CLK_EN_OFFSET 2 |

| #define BUS_CLK_GATING2_REG 0x00000088 |

| #define BUS_CLK_GATING2_REG_AHB_MONITOR_EN_CLEAR_MASK (0x00000100) |

| #define BUS_CLK_GATING2_REG_AHB_MONITOR_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_AHB_MONITOR_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_AHB_MONITOR_EN_OFFSET 8 |

| #define BUS_CLK_GATING2_REG_DE_CLKEN_CLEAR_MASK (0x00000002) |

| #define BUS_CLK_GATING2_REG_DE_CLKEN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_DE_CLKEN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_DE_CLKEN_OFFSET 1 |

| #define BUS_CLK_GATING2_REG_DE_HB_CLK_EN_CLEAR_MASK (0x00000001) |

| #define BUS_CLK_GATING2_REG_DE_HB_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_DE_HB_CLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_DE_HB_CLK_EN_OFFSET 0 |

| #define BUS_CLK_GATING2_REG_MCSI_HCLK_EN_CLEAR_MASK (0x10000000) |

| #define BUS_CLK_GATING2_REG_MCSI_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_MCSI_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_MCSI_HCLK_EN_OFFSET 28 |

| #define BUS_CLK_GATING2_REG_MCSI_SCLK_EN_CLEAR_MASK (0x08000000) |

| #define BUS_CLK_GATING2_REG_MCSI_SCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_MCSI_SCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_MCSI_SCLK_EN_OFFSET 27 |

| #define BUS_CLK_GATING2_REG_MISP_SCLK_EN_CLEAR_MASK (0x04000000) |

| #define BUS_CLK_GATING2_REG_MISP_SCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_MISP_SCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_MISP_SCLK_EN_OFFSET 26 |

| #define BUS_CLK_GATING2_REG_RES_DCAP_24M_EN_CLEAR_MASK (0x00000400) |

| #define BUS_CLK_GATING2_REG_RES_DCAP_24M_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_RES_DCAP_24M_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_RES_DCAP_24M_EN_OFFSET 10 |

| #define BUS_CLK_GATING2_REG_SD_MONITOR_EN_CLEAR_MASK (0x00000200) |

| #define BUS_CLK_GATING2_REG_SD_MONITOR_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_SD_MONITOR_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_SD_MONITOR_EN_OFFSET 9 |

| #define BUS_CLK_GATING2_REG_SGDMA_MCLK_EN_CLEAR_MASK (0x00000004) |

| #define BUS_CLK_GATING2_REG_SGDMA_MCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_SGDMA_MCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_SGDMA_MCLK_EN_OFFSET 2 |

| #define BUS_CLK_GATING2_REG_TCON_HCLK_EN_CLEAR_MASK (0x00000008) |

| #define BUS_CLK_GATING2_REG_TCON_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_TCON_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_TCON_HCLK_EN_OFFSET 3 |

| #define BUS_CLK_GATING2_REG_VE_HCLK_EN_CLEAR_MASK (0x00000010) |

| #define BUS_CLK_GATING2_REG_VE_HCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_VE_HCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_VE_HCLK_EN_OFFSET 4 |

| #define BUS_CLK_GATING2_REG_VE_SCLK_EN_CLEAR_MASK (0x00000020) |

| #define BUS_CLK_GATING2_REG_VE_SCLK_EN_CLOCK_IS_OFF 0b0 |

| #define BUS_CLK_GATING2_REG_VE_SCLK_EN_CLOCK_IS_ON 0b1 |

| #define BUS_CLK_GATING2_REG_VE_SCLK_EN_OFFSET 5 |

| #define BUS_CLK_GATING_REG 0x00000550 |

| #define BUS_CLK_GATING_REG_PWRCTRL_PCLK_EN_CLEAR_MASK (0x00000040) |

| #define BUS_CLK_GATING_REG_PWRCTRL_PCLK_EN_MASK 0b0 |

| #define BUS_CLK_GATING_REG_PWRCTRL_PCLK_EN_OFFSET 6 |

| #define BUS_CLK_GATING_REG_PWRCTRL_PCLK_EN_PASS 0b1 |

| #define BUS_CLK_GATING_REG_RCCAL_PCLK_EN_CLEAR_MASK (0x00000004) |

| #define BUS_CLK_GATING_REG_RCCAL_PCLK_EN_MASK 0b0 |

| #define BUS_CLK_GATING_REG_RCCAL_PCLK_EN_OFFSET 2 |

| #define BUS_CLK_GATING_REG_RCCAL_PCLK_EN_PASS 0b1 |

| #define BUS_Reset0_REG 0x00000090 |

| #define BUS_Reset0_REG_DPSS_TOP_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_DPSS_TOP_RSTN_SW_CLEAR_MASK (0x80000000) |

| #define BUS_Reset0_REG_DPSS_TOP_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_DPSS_TOP_RSTN_SW_OFFSET 31 |

| #define BUS_Reset0_REG_DRAM_ASSERT 0b0 |

| #define BUS_Reset0_REG_DRAM_CLEAR_MASK (0x00000008) |

| #define BUS_Reset0_REG_DRAM_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_DRAM_OFFSET 3 |

| #define BUS_Reset0_REG_HRESETN_CE_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_CE_SW_CLEAR_MASK (0x00000040) |

| #define BUS_Reset0_REG_HRESETN_CE_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_CE_SW_OFFSET 6 |

| #define BUS_Reset0_REG_HRESETN_DE_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_DE_SW_CLEAR_MASK (0x02000000) |

| #define BUS_Reset0_REG_HRESETN_DE_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_DE_SW_OFFSET 25 |

| #define BUS_Reset0_REG_HRESETN_DMA_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_DMA_SW_CLEAR_MASK (0x00000100) |

| #define BUS_Reset0_REG_HRESETN_DMA_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_DMA_SW_OFFSET 8 |

| #define BUS_Reset0_REG_HRESETN_G2D_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_G2D_SW_CLEAR_MASK (0x04000000) |

| #define BUS_Reset0_REG_HRESETN_G2D_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_G2D_SW_OFFSET 26 |

| #define BUS_Reset0_REG_HRESETN_GMAC_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_GMAC_SW_CLEAR_MASK (0x01000000) |

| #define BUS_Reset0_REG_HRESETN_GMAC_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_GMAC_SW_OFFSET 24 |

| #define BUS_Reset0_REG_HRESETN_HSTIMER_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_HSTIMER_SW_CLEAR_MASK (0x00000020) |

| #define BUS_Reset0_REG_HRESETN_HSTIMER_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_HSTIMER_SW_OFFSET 5 |

| #define BUS_Reset0_REG_HRESETN_MCSI_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_MCSI_SW_CLEAR_MASK (0x08000000) |

| #define BUS_Reset0_REG_HRESETN_MCSI_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_MCSI_SW_OFFSET 27 |

| #define BUS_Reset0_REG_HRESETN_SGDMA_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_SGDMA_SW_CLEAR_MASK (0x00000200) |

| #define BUS_Reset0_REG_HRESETN_SGDMA_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_SGDMA_SW_OFFSET 9 |

| #define BUS_Reset0_REG_HRESETN_SPLOCK_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_SPLOCK_SW_CLEAR_MASK (0x00000010) |

| #define BUS_Reset0_REG_HRESETN_SPLOCK_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_SPLOCK_SW_OFFSET 4 |

| #define BUS_Reset0_REG_HRESETN_SYSCTRL_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_SYSCTRL_SW_CLEAR_MASK (0x00000080) |

| #define BUS_Reset0_REG_HRESETN_SYSCTRL_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_SYSCTRL_SW_OFFSET 7 |

| #define BUS_Reset0_REG_HRESETN_USB_EHCI_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_USB_EHCI_SW_CLEAR_MASK (0x00200000) |

| #define BUS_Reset0_REG_HRESETN_USB_EHCI_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_USB_EHCI_SW_OFFSET 21 |

| #define BUS_Reset0_REG_HRESETN_USB_OHCI_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_USB_OHCI_SW_CLEAR_MASK (0x00400000) |

| #define BUS_Reset0_REG_HRESETN_USB_OHCI_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_USB_OHCI_SW_OFFSET 22 |

| #define BUS_Reset0_REG_HRESETN_USB_OTG_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_USB_OTG_SW_CLEAR_MASK (0x00100000) |

| #define BUS_Reset0_REG_HRESETN_USB_OTG_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_USB_OTG_SW_OFFSET 20 |

| #define BUS_Reset0_REG_HRESETN_USB_PHY_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_USB_PHY_SW_CLEAR_MASK (0x00800000) |

| #define BUS_Reset0_REG_HRESETN_USB_PHY_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_USB_PHY_SW_OFFSET 23 |

| #define BUS_Reset0_REG_HRESETN_USB_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_HRESETN_USB_SW_CLEAR_MASK (0x00080000) |

| #define BUS_Reset0_REG_HRESETN_USB_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_HRESETN_USB_SW_OFFSET 19 |

| #define BUS_Reset0_REG_MCSI_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_MCSI_RSTN_SW_CLEAR_MASK (0x10000000) |

| #define BUS_Reset0_REG_MCSI_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_MCSI_RSTN_SW_OFFSET 28 |

| #define BUS_Reset0_REG_PRESETN_PWM_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_PWM_SW_CLEAR_MASK (0x00002000) |

| #define BUS_Reset0_REG_PRESETN_PWM_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_PWM_SW_OFFSET 13 |

| #define BUS_Reset0_REG_PRESETN_TIMER_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_TIMER_SW_CLEAR_MASK (0x00000400) |

| #define BUS_Reset0_REG_PRESETN_TIMER_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_TIMER_SW_OFFSET 10 |

| #define BUS_Reset0_REG_PRESETN_TRNG_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_TRNG_SW_CLEAR_MASK (0x00000800) |

| #define BUS_Reset0_REG_PRESETN_TRNG_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_TRNG_SW_OFFSET 11 |

| #define BUS_Reset0_REG_PRESETN_TWI0_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_TWI0_SW_CLEAR_MASK (0x00004000) |

| #define BUS_Reset0_REG_PRESETN_TWI0_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_TWI0_SW_OFFSET 14 |

| #define BUS_Reset0_REG_PRESETN_UART0_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_UART0_SW_CLEAR_MASK (0x00008000) |

| #define BUS_Reset0_REG_PRESETN_UART0_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_UART0_SW_OFFSET 15 |

| #define BUS_Reset0_REG_PRESETN_UART1_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_UART1_SW_CLEAR_MASK (0x00010000) |

| #define BUS_Reset0_REG_PRESETN_UART1_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_UART1_SW_OFFSET 16 |

| #define BUS_Reset0_REG_PRESETN_UART2_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_UART2_SW_CLEAR_MASK (0x00020000) |

| #define BUS_Reset0_REG_PRESETN_UART2_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_UART2_SW_OFFSET 17 |

| #define BUS_Reset0_REG_PRESETN_UART3_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_UART3_SW_CLEAR_MASK (0x00040000) |

| #define BUS_Reset0_REG_PRESETN_UART3_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_UART3_SW_OFFSET 18 |

| #define BUS_Reset0_REG_PRESETN_WIEGAND_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_PRESETN_WIEGAND_SW_CLEAR_MASK (0x00001000) |

| #define BUS_Reset0_REG_PRESETN_WIEGAND_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_PRESETN_WIEGAND_SW_OFFSET 12 |

| #define BUS_Reset0_REG_RV_CFG_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_RV_CFG_RSTN_SW_CLEAR_MASK (0x00000001) |

| #define BUS_Reset0_REG_RV_CFG_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_RV_CFG_RSTN_SW_OFFSET 0 |

| #define BUS_Reset0_REG_RV_MSGBOX_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_RV_MSGBOX_RSTN_SW_CLEAR_MASK (0x00000004) |

| #define BUS_Reset0_REG_RV_MSGBOX_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_RV_MSGBOX_RSTN_SW_OFFSET 2 |

| #define BUS_Reset0_REG_RV_SYS_APB_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_RV_SYS_APB_RSTN_SW_CLEAR_MASK (0x00000002) |

| #define BUS_Reset0_REG_RV_SYS_APB_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_RV_SYS_APB_RSTN_SW_OFFSET 1 |

| #define BUS_Reset0_REG_WKUP_TMR_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset0_REG_WKUP_TMR_RSTN_SW_CLEAR_MASK (0x20000000) |

| #define BUS_Reset0_REG_WKUP_TMR_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset0_REG_WKUP_TMR_RSTN_SW_OFFSET 29 |

| #define BUS_Reset1_REG 0x00000094 |

| #define BUS_Reset1_REG_A27_CFG_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_A27_CFG_RSTN_SW_CLEAR_MASK (0x10000000) |

| #define BUS_Reset1_REG_A27_CFG_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_A27_CFG_RSTN_SW_OFFSET 28 |

| #define BUS_Reset1_REG_A27_MSGBOX_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_A27_MSGBOX_RSTN_SW_CLEAR_MASK (0x08000000) |

| #define BUS_Reset1_REG_A27_MSGBOX_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_A27_MSGBOX_RSTN_SW_OFFSET 27 |

| #define BUS_Reset1_REG_A27_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_A27_RSTN_SW_CLEAR_MASK (0x04000000) |

| #define BUS_Reset1_REG_A27_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_A27_RSTN_SW_OFFSET 26 |

| #define BUS_Reset1_REG_DBGSYS_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_DBGSYS_RSTN_SW_CLEAR_MASK (0x00040000) |

| #define BUS_Reset1_REG_DBGSYS_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_DBGSYS_RSTN_SW_OFFSET 18 |

| #define BUS_Reset1_REG_GPA_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_GPA_RSTN_SW_CLEAR_MASK (0x00000001) |

| #define BUS_Reset1_REG_GPA_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_GPA_RSTN_SW_OFFSET 0 |

| #define BUS_Reset1_REG_HRESETN_AUDIO_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_AUDIO_SW_CLEAR_MASK (0x00000040) |

| #define BUS_Reset1_REG_HRESETN_AUDIO_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_AUDIO_SW_OFFSET 6 |

| #define BUS_Reset1_REG_HRESETN_DMIC_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_DMIC_SW_CLEAR_MASK (0x00000080) |

| #define BUS_Reset1_REG_HRESETN_DMIC_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_DMIC_SW_OFFSET 7 |

| #define BUS_Reset1_REG_HRESETN_I2S0_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_I2S0_SW_CLEAR_MASK (0x00000100) |

| #define BUS_Reset1_REG_HRESETN_I2S0_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_I2S0_SW_OFFSET 8 |

| #define BUS_Reset1_REG_HRESETN_I2S1_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_I2S1_SW_CLEAR_MASK (0x00000200) |

| #define BUS_Reset1_REG_HRESETN_I2S1_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_I2S1_SW_OFFSET 9 |

| #define BUS_Reset1_REG_HRESETN_SMHC0_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SMHC0_SW_CLEAR_MASK (0x00100000) |

| #define BUS_Reset1_REG_HRESETN_SMHC0_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SMHC0_SW_OFFSET 20 |

| #define BUS_Reset1_REG_HRESETN_SMHC1_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SMHC1_SW_CLEAR_MASK (0x00200000) |

| #define BUS_Reset1_REG_HRESETN_SMHC1_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SMHC1_SW_OFFSET 21 |

| #define BUS_Reset1_REG_HRESETN_SPI1_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SPI1_SW_CLEAR_MASK (0x00080000) |

| #define BUS_Reset1_REG_HRESETN_SPI1_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SPI1_SW_OFFSET 19 |

| #define BUS_Reset1_REG_HRESETN_SPI2_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SPI2_SW_CLEAR_MASK (0x00800000) |

| #define BUS_Reset1_REG_HRESETN_SPI2_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SPI2_SW_OFFSET 23 |

| #define BUS_Reset1_REG_HRESETN_SPI_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SPI_SW_CLEAR_MASK (0x00000010) |

| #define BUS_Reset1_REG_HRESETN_SPI_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SPI_SW_OFFSET 4 |

| #define BUS_Reset1_REG_HRESETN_SPIF_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_HRESETN_SPIF_SW_CLEAR_MASK (0x00000020) |

| #define BUS_Reset1_REG_HRESETN_SPIF_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_HRESETN_SPIF_SW_OFFSET 5 |

| #define BUS_Reset1_REG_MBUS_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_MBUS_RSTN_SW_CLEAR_MASK (0x00001000) |

| #define BUS_Reset1_REG_MBUS_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_MBUS_RSTN_SW_OFFSET 12 |

| #define BUS_Reset1_REG_PRESETN_TWI1_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_PRESETN_TWI1_SW_CLEAR_MASK (0x01000000) |

| #define BUS_Reset1_REG_PRESETN_TWI1_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_PRESETN_TWI1_SW_OFFSET 24 |

| #define BUS_Reset1_REG_PRESETN_TWI2_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_PRESETN_TWI2_SW_CLEAR_MASK (0x02000000) |

| #define BUS_Reset1_REG_PRESETN_TWI2_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_PRESETN_TWI2_SW_OFFSET 25 |

| #define BUS_Reset1_REG_TCON_LCD_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_TCON_LCD_RSTN_SW_CLEAR_MASK (0x00000800) |

| #define BUS_Reset1_REG_TCON_LCD_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_TCON_LCD_RSTN_SW_OFFSET 11 |

| #define BUS_Reset1_REG_THS_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_THS_RSTN_SW_CLEAR_MASK (0x00000002) |

| #define BUS_Reset1_REG_THS_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_THS_RSTN_SW_OFFSET 1 |

| #define BUS_Reset1_REG_VE_RSTN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_VE_RSTN_SW_CLEAR_MASK (0x00000008) |

| #define BUS_Reset1_REG_VE_RSTN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_VE_RSTN_SW_OFFSET 3 |

| #define BUS_Reset1_REG_VO0_HRESETN_SW_ASSERT 0b0 |

| #define BUS_Reset1_REG_VO0_HRESETN_SW_CLEAR_MASK (0x00000400) |

| #define BUS_Reset1_REG_VO0_HRESETN_SW_DE_ASSERT 0b1 |

| #define BUS_Reset1_REG_VO0_HRESETN_SW_OFFSET 10 |

| #define CCM_SPIF_CTRL_ENABLE (0x1 << 31) |

| #define CCM_SPIF_CTRL_HOSC (0x0 << 24) |

| #define CCM_SPIF_CTRL_M | ( | x | ) | ((x) -1) |

| #define CCM_SPIF_CTRL_N | ( | x | ) | ((x) << 16) |

| #define CCM_SPIF_CTRL_PERI CCM_SPIF_CTRL_PERI384M |

| #define CCM_SPIF_CTRL_PERI307M (0x3 << 24) |

| #define CCM_SPIF_CTRL_PERI384M (0x2 << 24) |

| #define CCM_SPIF_CTRL_PERI512M (0x1 << 24) |

| #define CCU_A27_CLK_CPU_M_1 (0) |

| #define CCU_A27_CLK_CPU_M_2 (1) |

| #define CCU_A27_CLK_CPU_M_3 (2) |

| #define CCU_A27_CLK_REG (SUNXI_CCM_AON_BASE + A27L2_CLK_REG) |

| #define CCU_A27L2_MTCLK_EN (A27L2_MT_CLK_EN_CLOCK_IS_ON << REG_A27L2_MT_CLK_EN_OFFSET) |

| #define CCU_A27L2_MTCLK_REG (A27L2_MT_Clock_REG) |

| #define CCU_AHB_CLK_REG (SUNXI_CCM_AON_BASE + AHB_CLK_REG) |

| #define CCU_AON_PLL_CPU_D_1 (0) |

| #define CCU_AON_PLL_CPU_D_2 (1) |

| #define CCU_AON_PLL_CPU_D_4 (3) |

| #define CCU_AON_PLL_CPU_M_1 (0) |

| #define CCU_AON_PLL_CPU_M_2 (1) |

| #define CCU_AON_PLL_CPU_M_3 (2) |

| #define CCU_AON_PLL_CPU_M_4 (3) |

| #define CCU_AON_PLL_CPU_M_5 (4) |

| #define CCU_AON_PLL_CPU_N_118 (117) |

| #define CCU_AON_PLL_CPU_N_192 (191) |

| #define CCU_AON_PLL_CPU_N_24 (23) |

| #define CCU_AON_PLL_CPU_N_25 (24) |

| #define CCU_AON_PLL_CPU_N_27 (26) |

| #define CCU_AON_PLL_CPU_N_30 (29) |

| #define CCU_AON_PLL_CPU_N_40 (39) |

| #define CCU_AON_PLL_CPU_N_41 (40) |

| #define CCU_AON_PLL_CPU_N_45 (44) |

| #define CCU_AON_PLL_CPU_N_50 (49) |

| #define CCU_AON_PLL_CPU_N_56 (55) |

| #define CCU_AON_PLL_CPU_N_67 (66) |

| #define CCU_AON_PLL_CPU_N_96 (95) |

| #define CCU_AON_PLL_CPU_N_99 (98) |

| #define CCU_APB_CLK_REG (SUNXI_CCM_AON_BASE + APB_CLK_REG) |

| #define CCU_APB_SPEC_CLK_REG (SUNXI_CCM_AON_BASE + APB_SPEC_CLK_REG) |

| #define CCU_APP_CLK_REG 0x0000007c |

| #define CCU_APP_CLK_REG_A27_MSGBOX_HCLKEN_CLEAR_MASK (0x00000040) |

| #define CCU_APP_CLK_REG_A27_MSGBOX_HCLKEN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_A27_MSGBOX_HCLKEN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_A27_MSGBOX_HCLKEN_OFFSET 6 |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_CLEAR_MASK (0x00000300) |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_DIV1 0b00 |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_DIV2 0b01 |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_DIV3 0b10 |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_DIV4 0b11 |

| #define CCU_APP_CLK_REG_A27L2_BUSCLKDIV_OFFSET 8 |

| #define CCU_APP_CLK_REG_A27L2_CFG_CLKEN_CLEAR_MASK (0x00000080) |

| #define CCU_APP_CLK_REG_A27L2_CFG_CLKEN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_A27L2_CFG_CLKEN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_A27L2_CFG_CLKEN_OFFSET 7 |

| #define CCU_APP_CLK_REG_AVS_CLK_EN_CLEAR_MASK (0x00000001) |

| #define CCU_APP_CLK_REG_AVS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_AVS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_AVS_CLK_EN_OFFSET 0 |

| #define CCU_APP_CLK_REG_CLK12M_USB_EN_CLEAR_MASK (0x00000004) |

| #define CCU_APP_CLK_REG_CLK12M_USB_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_CLK12M_USB_EN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_CLK12M_USB_EN_OFFSET 2 |

| #define CCU_APP_CLK_REG_CLK24M_USB_EN_CLEAR_MASK (0x00000008) |

| #define CCU_APP_CLK_REG_CLK24M_USB_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_CLK24M_USB_EN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_CLK24M_USB_EN_OFFSET 3 |

| #define CCU_APP_CLK_REG_CLK48M_USB_EN_CLEAR_MASK (0x00000002) |

| #define CCU_APP_CLK_REG_CLK48M_USB_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_CLK48M_USB_EN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_CLK48M_USB_EN_OFFSET 1 |

| #define CCU_APP_CLK_REG_WIEGAND_24M_EN_CLEAR_MASK (0x00000010) |

| #define CCU_APP_CLK_REG_WIEGAND_24M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_APP_CLK_REG_WIEGAND_24M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_APP_CLK_REG_WIEGAND_24M_EN_OFFSET 4 |

| #define CCU_BASE (SUNXI_CCU_BASE) |

| #define CCU_BUS_CLK_GATING0_REG (BUS_CLK_GATING0_REG) |

| #define CCU_BUS_Reset0_REG (BUS_Reset0_REG) |

| #define CCU_E907_CFG_CLK_GATING (0x1 << 0) |

| #define CCU_E907_CFG_RST (0x1 << 0) |

| #define CCU_E907_RSTN_REG (E907_RSTN_REG) |

| #define CCU_E907_SYS_APB_RST (0x1 << 1) |

| #define CCU_E90X_CLK_CPU_M_1 (0) |

| #define CCU_E90X_CLK_CPU_M_2 (1) |

| #define CCU_E90X_CLK_REG (SUNXI_CCM_AON_BASE + E907_CLK_REG) |

| #define CCU_FUNC_CFG_REG (SUNXI_CCM_AON_BASE + PLL_FUNC_CFG_REG) |

| #define CCU_GPADC_BGR_REG (GPADC_CLK_REG) |

| #define CCU_HOSC_FREQ_DET_REG (SUNXI_CCM_AON_BASE + HOSC_FREQ_DET) |

| #define CCU_PLL_CPU_BIAS_REG (SUNXI_CCM_AON_BASE + PLL_CPU_BIAS_REG) |

| #define CCU_PLL_CPU_TUN_REG (SUNXI_CCM_AON_BASE + PLL_CPU_TUN_REG) |

| #define CCU_PLL_CPUX_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_CPU_CTRL_REG) |

| #define CCU_PLL_CSI_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_CSI_CTRL_REG) |

| #define CCU_PLL_CSI_PAT0_REG (SUNXI_CCM_AON_BASE + PLL_CSI_PAT0_CTRL_REG) |

| #define CCU_PLL_CSI_PAT1_REG (SUNXI_CCM_AON_BASE + PLL_CSI_PAT1_CTRL_REG) |

| #define CCU_PLL_DDR0_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_DDR_CTRL_REG) |

| #define CCU_PLL_DDR_BIAS_REG (SUNXI_CCM_AON_BASE + PLL_DDR_BIAS_REG) |

| #define CCU_PLL_DDR_PAT0_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_DDR_PAT0_CTRL_REG) |

| #define CCU_PLL_DDR_PAT1_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_DDR_PAT1_CTRL_REG) |

| #define CCU_PLL_FUNC_CFG_REG (SUNXI_CCM_AON_BASE + PLL_FUNC_CFG_REG) |

| #define CCU_PLL_PERI0_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_PERI_CTRL0_REG) |

| #define CCU_PLL_PERI1_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_PERI_CTRL1_REG) |

| #define CCU_PLL_PERI_BIAS_REG (SUNXI_CCM_AON_BASE + PLL_PERI_BIAS_REG) |

| #define CCU_PLL_PERI_CTRL0_REG (SUNXI_CCM_AON_BASE + PLL_PERI_CTRL0_REG) |

| #define CCU_PLL_PERI_CTRL1_REG (SUNXI_CCM_AON_BASE + PLL_PERI_CTRL1_REG) |

| #define CCU_PLL_PERI_PAT0_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_PERI_PAT0_CTRL_REG) |

| #define CCU_PLL_PERI_PAT1_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_PERI_PAT1_CTRL_REG) |

| #define CCU_PLL_VIDEO_CTRL_REG (SUNXI_CCM_AON_BASE + PLL_VIDEO_CTRL_REG) |

| #define CCU_SDMMC0_CLK_REG (SMHC_CTRL0_CLK_REG) |

| #define CCU_SDMMC1_CLK_REG (SMHC_CTRL1_CLK_REG) |

| #define CCU_SMHC0_BGR_REG_GATING (BUS_CLK_GATING1_REG) |

| #define CCU_SMHC0_BGR_REG_RESET (BUS_Reset1_REG) |

| #define CCU_SPI0_CLK_REG (SPI_CLK_REG) |

| #define CCU_SPI_BGR_REG (BUS_CLK_GATING0_REG) |

| #define CCU_UART_BGR_REG (BUS_CLK_GATING0_REG) |

| #define CCU_UART_RST_REG (BUS_Reset0_REG) |

| #define CK_TEST_DIV_REG 0x0000058c |

| #define CK_TEST_DIV_REG_CK_TEST_DIV1_CLEAR_MASK (0x0000001f) |

| #define CK_TEST_DIV_REG_CK_TEST_DIV1_OFFSET 0 |

| #define CK_TEST_DIV_REG_CK_TEST_DIV2_CLEAR_MASK (0x001f0000) |

| #define CK_TEST_DIV_REG_CK_TEST_DIV2_OFFSET 16 |

| #define CSI_MASTER0_CLK_REG 0x00000028 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV1_CLEAR_MASK (0x0000001f) |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV1_OFFSET 0 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_1 0b00 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_2 0b01 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_4 0b10 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_8 0b11 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_CLEAR_MASK (0x00030000) |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_DIV2_OFFSET 16 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_EN_CLEAR_MASK (0x80000000) |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_EN_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_EN_OFFSET 31 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_CSIPLL4X 0b001 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_HOSC 0b000 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_OFFSET 24 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_PERI_1024M 0b100 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_PERI_24M 0b101 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_SEL_VIDEOPLL4X 0b010 |

| #define CSI_MASTER1_CLK_REG 0x0000002c |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV1_CLEAR_MASK (0x0000001f) |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV1_OFFSET 0 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_1 0b00 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_2 0b01 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_4 0b10 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_8 0b11 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_CLEAR_MASK (0x00030000) |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_DIV2_OFFSET 16 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_EN_CLEAR_MASK (0x80000000) |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_EN_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_EN_OFFSET 31 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_CSIPLL4X 0b001 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_HOSC 0b000 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_OFFSET 24 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_PERI_1024M 0b100 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_PERI_24M 0b101 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_SEL_VIDEOPLL4X 0b010 |

| #define DCXO_CFG1_REG 0x00000574 |

| #define DCXO_CFG1_REG_DCXO_CNT_TG_CLEAR_MASK (0x00001fff) |

| #define DCXO_CFG1_REG_DCXO_CNT_TG_OFFSET 0 |

| #define DCXO_CFG1_REG_DCXO_DETECT_MD_CLEAR_MASK (0x00002000) |

| #define DCXO_CFG1_REG_DCXO_DETECT_MD_OFFSET 13 |

| #define DCXO_CFG_REG 0x00000570 |

| #define DCXO_CFG_REG_BG_V09_0 0x4 |

| #define DCXO_CFG_REG_BG_V09_CLEAR_MASK (0x0000007c) |

| #define DCXO_CFG_REG_BG_V09_OFFSET 2 |

| #define DCXO_CFG_REG_CLK_REQ_ENB_CLEAR_MASK (0x00400000) |

| #define DCXO_CFG_REG_CLK_REQ_ENB_DISABLE 0b1 |

| #define DCXO_CFG_REG_CLK_REQ_ENB_ENABLE 0b0 |

| #define DCXO_CFG_REG_CLK_REQ_ENB_OFFSET 22 |

| #define DCXO_CFG_REG_DCXO_FLAG_CLEAR_MASK (0x00000001) |

| #define DCXO_CFG_REG_DCXO_FLAG_DCXO_SOURCE_FROM_ADIE 0b0 |

| #define DCXO_CFG_REG_DCXO_FLAG_DCXO_SOURCE_FROM_DDIE 0b1 |

| #define DCXO_CFG_REG_DCXO_FLAG_OFFSET 0 |

| #define DCXO_CFG_REG_DCXO_ICTRL_V09_0 0x3 |

| #define DCXO_CFG_REG_DCXO_ICTRL_V09_CLEAR_MASK (0x00000780) |

| #define DCXO_CFG_REG_DCXO_ICTRL_V09_OFFSET 7 |

| #define DCXO_CFG_REG_DCXO_LDO_INRUSHB_V09_CLEAR_MASK (0x00040000) |

| #define DCXO_CFG_REG_DCXO_LDO_INRUSHB_V09_OFFSET 18 |

| #define DCXO_CFG_REG_DCXO_TRIM_V09_0 0x6 |

| #define DCXO_CFG_REG_DCXO_TRIM_V09_CLEAR_MASK (0x0003f800) |

| #define DCXO_CFG_REG_DCXO_TRIM_V09_OFFSET 11 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_0 0b1 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_15PF 0b01 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_22PF 0b10 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_30PF 0b11 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_8PF 0b00 |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_CLEAR_MASK (0x00300000) |

| #define DCXO_CFG_REG_ENHANCE_RF_CLK_OUT_V09_OFFSET 20 |

| #define DCXO_CFG_REG_MODE_SEL_MUX_CLEAR_MASK (0x00000002) |

| #define DCXO_CFG_REG_MODE_SEL_MUX_FROM_INPUT_XTAL_MODE_V09 0b1 |

| #define DCXO_CFG_REG_MODE_SEL_MUX_FROM_SEL_A_N 0b0 |

| #define DCXO_CFG_REG_MODE_SEL_MUX_OFFSET 1 |

| #define DCXO_CFG_REG_XTAL_MODE_V09_CLEAR_MASK (0x00080000) |

| #define DCXO_CFG_REG_XTAL_MODE_V09_FOR_EXTERNAL_CLK_D_DIE 0b0 |

| #define DCXO_CFG_REG_XTAL_MODE_V09_INPUT_MODE_A_DIE 0b1 |

| #define DCXO_CFG_REG_XTAL_MODE_V09_OFFSET 19 |

| #define DCXO_CNT_REG 0x00000510 |

| #define DCXO_CNT_REG_DIV32K_HALFCYCLE_TARGET_CLEAR_MASK (0x000003ff) |

| #define DCXO_CNT_REG_DIV32K_HALFCYCLE_TARGET_OFFSET 0 |

| #define DE_CLK_REG 0x00000038 |

| #define DE_CLK_REG_DE_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define DE_CLK_REG_DE_CLK_DIV_OFFSET 0 |

| #define DE_CLK_REG_DE_CLK_EN_CLEAR_MASK (0x80000000) |

| #define DE_CLK_REG_DE_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define DE_CLK_REG_DE_CLK_EN_CLOCK_IS_ON 0b1 |

| #define DE_CLK_REG_DE_CLK_EN_OFFSET 31 |

| #define DE_CLK_REG_DE_CLK_SEL_CLEAR_MASK (0x01000000) |

| #define DE_CLK_REG_DE_CLK_SEL_OFFSET 24 |

| #define DE_CLK_REG_DE_CLK_SEL_PERI_307M 0b0 |

| #define DE_CLK_REG_DE_CLK_SEL_VIDEOPLL1X 0b1 |

| #define DRAM_CLK_REG 0x00000004 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLEAR_MASK (0x80000000) |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_OFFSET 31 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_CLK_HOSC 0b000 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_DDRPLL 0b001 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_OFFSET 24 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI_1024M 0b010 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI_768M 0b011 |

| #define DRAM_CLK_REG_DRAM_DIV1_CLEAR_MASK (0x0000001f) |

| #define DRAM_CLK_REG_DRAM_DIV1_OFFSET 0 |

| #define DRAM_CLK_REG_DRAM_DIV2_1 0b00 |

| #define DRAM_CLK_REG_DRAM_DIV2_2 0b01 |

| #define DRAM_CLK_REG_DRAM_DIV2_4 0b10 |

| #define DRAM_CLK_REG_DRAM_DIV2_8 0b11 |

| #define DRAM_CLK_REG_DRAM_DIV2_CLEAR_MASK (0x00030000) |

| #define DRAM_CLK_REG_DRAM_DIV2_OFFSET 16 |

| #define DRAM_CLK_REG_DRAM_UPD_CLEAR_MASK (0x08000000) |

| #define DRAM_CLK_REG_DRAM_UPD_INVALID 0b0 |

| #define DRAM_CLK_REG_DRAM_UPD_OFFSET 27 |

| #define DRAM_CLK_REG_DRAM_UPD_VALID 0b1 |

| #define E907_CFG_BASE (0x43030000) |

| #define E907_CLK_REG 0x00000584 |

| #define E907_CLK_REG_E907_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define E907_CLK_REG_E907_CLK_DIV_OFFSET 0 |

| #define E907_CLK_REG_E907_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define E907_CLK_REG_E907_CLK_SEL_CPU_PLL 0b100 |

| #define E907_CLK_REG_E907_CLK_SEL_HOSC 0b000 |

| #define E907_CLK_REG_E907_CLK_SEL_OFFSET 24 |

| #define E907_CLK_REG_E907_CLK_SEL_PERI_PLL_1024M 0b101 |

| #define E907_CLK_REG_E907_CLK_SEL_PERI_PLL_614M 0b110 |

| #define E907_CLK_REG_E907_CLK_SEL_PERI_PLL_614M0 0b111 |

| #define E907_CLK_REG_E907_CLK_SEL_RC1M 0b010 |

| #define E907_CLK_REG_E907_CLK_SEL_RC1M0 0b011 |

| #define E907_CLK_REG_E907_CLK_SEL_VIDEOPLL2X 0b001 |

| #define E907_R_CLK_REG 0x00000068 |

| #define E907_R_CLK_REG_E907_RCLK_DIV_CLEAR_MASK (0x00000003) |

| #define E907_R_CLK_REG_E907_RCLK_DIV_DIV1 0b00 |

| #define E907_R_CLK_REG_E907_RCLK_DIV_DIV2 0b01 |

| #define E907_R_CLK_REG_E907_RCLK_DIV_DIV3 0b10 |

| #define E907_R_CLK_REG_E907_RCLK_DIV_DIV4 0b11 |

| #define E907_R_CLK_REG_E907_RCLK_DIV_OFFSET 0 |

| #define E907_RSTN_REG 0x0000009c |

| #define E907_RSTN_REG_E907_RSTN_SW_ASSERT 0b0 |

| #define E907_RSTN_REG_E907_RSTN_SW_CLEAR_MASK (0x00000001) |

| #define E907_RSTN_REG_E907_RSTN_SW_DE_ASSERT 0b1 |

| #define E907_RSTN_REG_E907_RSTN_SW_OFFSET 0 |

| #define E907_RSTN_REG_E907_RSTN_SW_WRITE_LOCK_CLEAR_MASK (0xffff0000) |

| #define E907_RSTN_REG_E907_RSTN_SW_WRITE_LOCK_OFFSET 16 |

| #define E907_STA_ADD_REG (E907_CFG_BASE + 0x0204) |

| #define E907_TS_CLK_EN_CLEAR_MASK (0x80000000) |

| #define E907_TS_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define E907_TS_CLK_EN_CLOCK_IS_ON 0b1 |

| #define E907_TS_CLK_EN_OFFSET 31 |

| #define E907_TS_CLK_SEL_CLEAR_MASK (0x01000000) |

| #define E907_TS_CLK_SEL_HOSC 0b0 |

| #define E907_TS_CLK_SEL_OFFSET 24 |

| #define E907_TS_CLK_SEL_SYS_32K 0b1 |

| #define E907_TS_Clock_REG 0x0000000c |

| #define G2D_CLK_REG 0x0000003c |

| #define G2D_CLK_REG_G2D_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define G2D_CLK_REG_G2D_CLK_DIV_OFFSET 0 |

| #define G2D_CLK_REG_G2D_CLK_EN_CLEAR_MASK (0x80000000) |

| #define G2D_CLK_REG_G2D_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define G2D_CLK_REG_G2D_CLK_EN_CLOCK_IS_ON 0b1 |

| #define G2D_CLK_REG_G2D_CLK_EN_OFFSET 31 |

| #define G2D_CLK_REG_G2D_CLK_SEL_CLEAR_MASK (0x01000000) |

| #define G2D_CLK_REG_G2D_CLK_SEL_OFFSET 24 |

| #define G2D_CLK_REG_G2D_CLK_SEL_PERI_307M 0b0 |

| #define G2D_CLK_REG_G2D_CLK_SEL_VIDEOPLL1X 0b1 |

| #define GATING_RESET_SHIFT (4) |

| #define GET_SPIF_CLK_SOURECS | ( | x | ) | (x == CCM_SPIF_CTRL_PERI512M ? 512000000 : 384000000) |

| #define GMAC_25M_CLK_REG 0x00000074 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_DIV1_CLEAR_MASK (0x0000001f) |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_DIV1_OFFSET 0 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_DIV2_CLEAR_MASK (0x001f0000) |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_DIV2_OFFSET 16 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_EN_CLEAR_MASK (0x80000000) |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_EN_OFFSET 31 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SEL_CLEAR_MASK (0x03000000) |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SEL_CPUPLL 0b10 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SEL_CSIPLL2X 0b01 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SEL_HOSC 0b00 |

| #define GMAC_25M_CLK_REG_GMAC_25M_CLK_SEL_OFFSET 24 |

| #define GMAC_CLK_FANOUT_REG 0x0000006c |

| #define GMAC_CLK_FANOUT_REG_GMAC_16M_SRCCLK_EN_CLEAR_MASK (0x00020000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_16M_SRCCLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_16M_SRCCLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_16M_SRCCLK_EN_OFFSET 17 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_CLK_SEL_CLEAR_MASK (0x00000010) |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_CLK_SEL_OFFSET 4 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_CLK_SEL_SOURCE_FROM_DCXO 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_CLK_SEL_SOURCE_FROM_PERIPLL_24M 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_SRCCLK_EN_CLEAR_MASK (0x00000008) |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_SRCCLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_SRCCLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_24M_SRCCLK_EN_OFFSET 3 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV1_CLEAR_MASK (0x00001f00) |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV1_OFFSET 8 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_1 0b00 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_2 0b01 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_4 0b10 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_8 0b11 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_CLEAR_MASK (0x00006000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_DIV2_OFFSET 13 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_SEL_CLEAR_MASK (0x000000c0) |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_SEL_OFFSET 6 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_SEL_SOURCE_FROM_CSIPLL4X 0b01 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_SEL_SOURCE_FROM_DCXO 0b10 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_CLK_SEL_SOURCE_FROM_VIDEOPLL1X 0b00 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_SRCCLK_EN_CLEAR_MASK (0x00000020) |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_SRCCLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_SRCCLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_27M_SRCCLK_EN_OFFSET 5 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_CLK_SEL_CLEAR_MASK (0x00010000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_CLK_SEL_OFFSET 16 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_CLK_SEL_SOURCE_FROM_DCXO_DIV_32K_APP 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_CLK_SEL_SOURCE_FROM_SYS_32K_APP 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_SRCCLK_EN_CLEAR_MASK (0x00008000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_SRCCLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_SRCCLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_32K_SRCCLK_EN_OFFSET 15 |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_CLK_DIV1_CLEAR_MASK (0x00f80000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_CLK_DIV1_OFFSET 19 |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_CLK_DIV2_CLEAR_MASK (0x1f000000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_CLK_DIV2_OFFSET 24 |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_SRCCLK_EN_CLEAR_MASK (0x00040000) |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_SRCCLK_EN_CLOCK_IS_OFF 0b0 |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_SRCCLK_EN_CLOCK_IS_ON 0b1 |

| #define GMAC_CLK_FANOUT_REG_GMAC_APB_SRCCLK_EN_OFFSET 18 |

| #define GPADC_CLK_REG 0x00000040 |

| #define GPADC_CLK_REG_GPADC_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define GPADC_CLK_REG_GPADC_CLK_DIV_OFFSET 0 |

| #define GPADC_CLK_REG_GPADC_CLK_EN_CLEAR_MASK (0x80000000) |

| #define GPADC_CLK_REG_GPADC_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define GPADC_CLK_REG_GPADC_CLK_EN_CLOCK_IS_ON 0b1 |

| #define GPADC_CLK_REG_GPADC_CLK_EN_OFFSET 31 |

| #define GPADC_CLK_REG_GPADC_CLK_SEL_CLEAR_MASK (0x03000000) |

| #define GPADC_CLK_REG_GPADC_CLK_SEL_CLK_24M 0b00 |

| #define GPADC_CLK_REG_GPADC_CLK_SEL_HOSC 0b01 |

| #define GPADC_CLK_REG_GPADC_CLK_SEL_OFFSET 24 |

| #define GPADC_CLK_REG_GPADC_CLK_SEL_SYS32K 0b10 |

| #define H_MTIME_REG (SUNXI_PLMT_BASE + 0x4) |

| #define HOSC_24M_COUNTER (46875) |

| #define HOSC_40M_COUNTER (78125) |

| #define HOSC_FREQ_24M (24) |

| #define HOSC_FREQ_40M (40) |

| #define HOSC_FREQ_DET 0x00000408 |

| #define HOSC_FREQ_DET_HOSC_CLEAR_MASK (0x00000001) |

| #define HOSC_FREQ_DET_HOSC_DISABLE_DETECT 0b0 |

| #define HOSC_FREQ_DET_HOSC_ENABLE_DETECT 0b1 |

| #define HOSC_FREQ_DET_HOSC_FREQ_DET_CLEAR_MASK (0x00fffff0) |

| #define HOSC_FREQ_DET_HOSC_FREQ_DET_OFFSET 4 |

| #define HOSC_FREQ_DET_HOSC_FREQ_READY_CLEAR_MASK (0x00000002) |

| #define HOSC_FREQ_DET_HOSC_FREQ_READY_OFFSET 1 |

| #define HOSC_FREQ_DET_HOSC_OFFSET 0 |

| #define L_MTIME_REG (SUNXI_PLMT_BASE) |

| #define MCSI_CLK_REG 0x00000024 |

| #define MCSI_CLK_REG_MCSI_CLK_DIV_CLEAR_MASK (0x0000001f) |

| #define MCSI_CLK_REG_MCSI_CLK_DIV_OFFSET 0 |

| #define MCSI_CLK_REG_MCSI_CLK_EN_CLEAR_MASK (0x80000000) |

| #define MCSI_CLK_REG_MCSI_CLK_EN_CLOCK_IS_OFF 0b0 |

| #define MCSI_CLK_REG_MCSI_CLK_EN_CLOCK_IS_ON 0b1 |

| #define MCSI_CLK_REG_MCSI_CLK_EN_OFFSET 31 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_CLEAR_MASK (0x07000000) |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_CSIPLL4X 0b101 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_OFFSET 24 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_PERI_236M 0b000 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_PERI_307M 0b001 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_PERI_384M 0b010 |

| #define MCSI_CLK_REG_MCSI_CLK_SEL_VIDEOPLL4X 0b100 |

| #define PLL_AUDIO_BIAS_REG 0x00000378 |

| #define PLL_AUDIO_BIAS_REG_PLL_CP_CLEAR_MASK (0x001f0000) |

| #define PLL_AUDIO_BIAS_REG_PLL_CP_OFFSET 16 |

| #define PLL_AUDIO_CTRL_REG 0x00000078 |

| #define PLL_AUDIO_CTRL_REG_LOCK_CLEAR_MASK (0x10000000) |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_CLEAR_MASK (0x20000000) |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_LOCK_ENABLE_OFFSET 29 |

| #define PLL_AUDIO_CTRL_REG_LOCK_LOCKED__IT_INDICATES_THAT_THE_PLL_HAS_BEEN_STABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_LOCK_OFFSET 28 |

| #define PLL_AUDIO_CTRL_REG_LOCK_UNLOCKED 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_CLEAR_MASK (0x80000000) |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_EN_OFFSET 31 |

| #define PLL_AUDIO_CTRL_REG_PLL_FACTOR_N_CLEAR_MASK (0x0000ff00) |

| #define PLL_AUDIO_CTRL_REG_PLL_FACTOR_N_OFFSET 8 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV_1 0b00 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV_2 0b01 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV_4 0b10 |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK (0x00000006) |

| #define PLL_AUDIO_CTRL_REG_PLL_INPUT_DIV_OFFSET 1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_CLEAR_MASK (0x40000000) |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LDO_EN_OFFSET 30 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_23_27_CLOCK_CYCLES 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_24_26_CLOCK_CYCLES 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_CLEAR_MASK (0x00000020) |

| #define PLL_AUDIO_CTRL_REG_PLL_LOCK_MDSEL_OFFSET 5 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_CLEAR_MASK (0x08000000) |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_OUTPUT_GATE_OFFSET 27 |

| #define PLL_AUDIO_CTRL_REG_PLL_P0_CLEAR_MASK (0x00070000) |

| #define PLL_AUDIO_CTRL_REG_PLL_P0_OFFSET 16 |

| #define PLL_AUDIO_CTRL_REG_PLL_P1_CLEAR_MASK (0x00700000) |

| #define PLL_AUDIO_CTRL_REG_PLL_P1_OFFSET 20 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_CLEAR_MASK (0x01000000) |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_DISABLE 0b0 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_ENABLE 0b1 |

| #define PLL_AUDIO_CTRL_REG_PLL_SDM_EN_OFFSET 24 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_20_30_CLOCK_CYCLES 0b10 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_21_29_CLOCK_CYCLES 0b00 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_22_28_CLOCK_CYCLES 0b01 |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_CLEAR_MASK (0x000000c0) |

| #define PLL_AUDIO_CTRL_REG_PLL_UNLOCK_MDSEL_OFFSET 6 |

| #define PLL_AUDIO_PAT0_CTRL_REG 0x00000178 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_31_5KHZ 0b00 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_32_5KHZ 0b10 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_32KHZ 0b01 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_33KHZ 0b11 |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_CLEAR_MASK (0x00060000) |

| #define PLL_AUDIO_PAT0_CTRL_REG_FREQ_OFFSET 17 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_10MHZ 0b10 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_20MHZ 0b01 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_40MHZ 0b00 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_CLEAR_MASK (0x00180000) |

| #define PLL_AUDIO_PAT0_CTRL_REG_SDM_CLK_SEL_OFFSET 19 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_CLEAR_MASK (0xc0000000) |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_0 0b00 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_1 0b01 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_OFFSET 30 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_1BIT 0b10 |

| #define PLL_AUDIO_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_NBIT 0b11 |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_BOT_CLEAR_MASK (0x0001ffff) |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_BOT_OFFSET 0 |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_STEP_CLEAR_MASK (0x3fe00000) |

| #define PLL_AUDIO_PAT0_CTRL_REG_WAVE_STEP_OFFSET 21 |

| #define PLL_AUDIO_PAT1_CTRL_REG 0x0000017c |

| #define PLL_AUDIO_PAT1_CTRL_REG_DITHER_EN_CLEAR_MASK (0x01000000) |

| #define PLL_AUDIO_PAT1_CTRL_REG_DITHER_EN_OFFSET 24 |

| #define PLL_AUDIO_PAT1_CTRL_REG_FRAC_EN_CLEAR_MASK (0x00100000) |

| #define PLL_AUDIO_PAT1_CTRL_REG_FRAC_EN_OFFSET 20 |

| #define PLL_AUDIO_PAT1_CTRL_REG_FRAC_IN_CLEAR_MASK (0x0001ffff) |

| #define PLL_AUDIO_PAT1_CTRL_REG_FRAC_IN_OFFSET 0 |

| #define PLL_AUDIO_PAT1_CTRL_REG_SIG_DELT_PAT_EN_CLEAR_MASK (0x80000000) |

| #define PLL_AUDIO_PAT1_CTRL_REG_SIG_DELT_PAT_EN_OFFSET 31 |

| #define PLL_CPU_BIAS_REG 0x00000300 |

| #define PLL_CPU_BIAS_REG_PLL_CP_CLEAR_MASK (0x001f0000) |

| #define PLL_CPU_BIAS_REG_PLL_CP_OFFSET 16 |

| #define PLL_CPU_BIAS_REG_PLL_VCO_RST_IN_CLEAR_MASK (0x80000000) |

| #define PLL_CPU_BIAS_REG_PLL_VCO_RST_IN_OFFSET 31 |

| #define PLL_CPU_CTRL_REG 0x00000000 |

| #define PLL_CPU_CTRL_REG_LOCK_CLEAR_MASK (0x10000000) |

| #define PLL_CPU_CTRL_REG_LOCK_ENABLE_CLEAR_MASK (0x20000000) |

| #define PLL_CPU_CTRL_REG_LOCK_ENABLE_DISABLE 0b0 |

| #define PLL_CPU_CTRL_REG_LOCK_ENABLE_ENABLE 0b1 |

| #define PLL_CPU_CTRL_REG_LOCK_ENABLE_OFFSET 29 |

| #define PLL_CPU_CTRL_REG_LOCK_LOCKED__IT_INDICATES_THAT_THE_PLL_HAS_BEEN_STABLE 0b1 |

| #define PLL_CPU_CTRL_REG_LOCK_OFFSET 28 |

| #define PLL_CPU_CTRL_REG_LOCK_UNLOCKED 0b0 |

| #define PLL_CPU_CTRL_REG_PLL_EN_CLEAR_MASK (0x80000000) |

| #define PLL_CPU_CTRL_REG_PLL_EN_DISABLE 0b0 |

| #define PLL_CPU_CTRL_REG_PLL_EN_ENABLE 0b1 |

| #define PLL_CPU_CTRL_REG_PLL_EN_OFFSET 31 |

| #define PLL_CPU_CTRL_REG_PLL_INPUT_DIV_1 0b00 |

| #define PLL_CPU_CTRL_REG_PLL_INPUT_DIV_2 0b01 |

| #define PLL_CPU_CTRL_REG_PLL_INPUT_DIV_4 0b10 |

| #define PLL_CPU_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK (0x0000000c) |

| #define PLL_CPU_CTRL_REG_PLL_INPUT_DIV_OFFSET 2 |

| #define PLL_CPU_CTRL_REG_PLL_LDO_EN_CLEAR_MASK (0x40000000) |

| #define PLL_CPU_CTRL_REG_PLL_LDO_EN_DISABLE 0b0 |

| #define PLL_CPU_CTRL_REG_PLL_LDO_EN_ENABLE 0b1 |

| #define PLL_CPU_CTRL_REG_PLL_LDO_EN_OFFSET 30 |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_MDSEL_23_27_CLOCK_CYCLES 0b1 |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_MDSEL_24_26_CLOCK_CYCLES 0b0 |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_MDSEL_CLEAR_MASK (0x00000020) |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_MDSEL_OFFSET 5 |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_TIME_CLEAR_MASK (0x07000000) |

| #define PLL_CPU_CTRL_REG_PLL_LOCK_TIME_OFFSET 24 |

| #define PLL_CPU_CTRL_REG_PLL_M_CLEAR_MASK (0x00000003) |

| #define PLL_CPU_CTRL_REG_PLL_M_OFFSET 0 |

| #define PLL_CPU_CTRL_REG_PLL_N_CLEAR_MASK (0x0000ff00) |

| #define PLL_CPU_CTRL_REG_PLL_N_OFFSET 8 |

| #define PLL_CPU_CTRL_REG_PLL_OUTPUT_GATE_CLEAR_MASK (0x08000000) |

| #define PLL_CPU_CTRL_REG_PLL_OUTPUT_GATE_DISABLE 0b0 |

| #define PLL_CPU_CTRL_REG_PLL_OUTPUT_GATE_ENABLE 0b1 |

| #define PLL_CPU_CTRL_REG_PLL_OUTPUT_GATE_OFFSET 27 |

| #define PLL_CPU_CTRL_REG_PLL_UNLOCK_MDSEL_20_30_CLOCK_CYCLES 0b10 |

| #define PLL_CPU_CTRL_REG_PLL_UNLOCK_MDSEL_21_29_CLOCK_CYCLES 0b00 |

| #define PLL_CPU_CTRL_REG_PLL_UNLOCK_MDSEL_22_28_CLOCK_CYCLES 0b01 |

| #define PLL_CPU_CTRL_REG_PLL_UNLOCK_MDSEL_CLEAR_MASK (0x000000c0) |

| #define PLL_CPU_CTRL_REG_PLL_UNLOCK_MDSEL_OFFSET 6 |

| #define PLL_CPU_TUN_REG 0x00000400 |

| #define PLL_CPU_TUN_REG_PLL_B_IN_CLEAR_MASK (0x00007f00) |

| #define PLL_CPU_TUN_REG_PLL_B_IN_OFFSET 8 |

| #define PLL_CPU_TUN_REG_PLL_B_OUT_CLEAR_MASK (0x0000007f) |

| #define PLL_CPU_TUN_REG_PLL_B_OUT_OFFSET 0 |

| #define PLL_CPU_TUN_REG_PLL_CNT_INT_CLEAR_MASK (0x007f0000) |

| #define PLL_CPU_TUN_REG_PLL_CNT_INT_OFFSET 16 |

| #define PLL_CPU_TUN_REG_PLL_REG_OD1_CLEAR_MASK (0x00000080) |

| #define PLL_CPU_TUN_REG_PLL_REG_OD1_OFFSET 7 |

| #define PLL_CPU_TUN_REG_PLL_REG_OD_CLEAR_MASK (0x00008000) |

| #define PLL_CPU_TUN_REG_PLL_REG_OD_OFFSET 15 |

| #define PLL_CPU_TUN_REG_PLL_VCO_CLEAR_MASK (0x70000000) |

| #define PLL_CPU_TUN_REG_PLL_VCO_GAIN_CLEAR_MASK (0x07000000) |

| #define PLL_CPU_TUN_REG_PLL_VCO_GAIN_OFFSET 24 |

| #define PLL_CPU_TUN_REG_PLL_VCO_OFFSET 28 |

| #define PLL_CSI_BIAS_REG 0x00000348 |

| #define PLL_CSI_BIAS_REG_PLL_CP_CLEAR_MASK (0x001f0000) |

| #define PLL_CSI_BIAS_REG_PLL_CP_OFFSET 16 |

| #define PLL_CSI_CTRL_REG 0x00000048 |

| #define PLL_CSI_CTRL_REG_LOCK_CLEAR_MASK (0x10000000) |

| #define PLL_CSI_CTRL_REG_LOCK_ENABLE_CLEAR_MASK (0x20000000) |

| #define PLL_CSI_CTRL_REG_LOCK_ENABLE_DISABLE 0b0 |

| #define PLL_CSI_CTRL_REG_LOCK_ENABLE_ENABLE 0b1 |

| #define PLL_CSI_CTRL_REG_LOCK_ENABLE_OFFSET 29 |

| #define PLL_CSI_CTRL_REG_LOCK_LOCKED__IT_INDICATES_THAT_THE_PLL_HAS_BEEN_STABLE 0b1 |

| #define PLL_CSI_CTRL_REG_LOCK_OFFSET 28 |

| #define PLL_CSI_CTRL_REG_LOCK_UNLOCKED 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_EN_CLEAR_MASK (0x80000000) |

| #define PLL_CSI_CTRL_REG_PLL_EN_DISABLE 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_EN_ENABLE 0b1 |

| #define PLL_CSI_CTRL_REG_PLL_EN_OFFSET 31 |

| #define PLL_CSI_CTRL_REG_PLL_FACTOR_N_CLEAR_MASK (0x0000ff00) |

| #define PLL_CSI_CTRL_REG_PLL_FACTOR_N_OFFSET 8 |

| #define PLL_CSI_CTRL_REG_PLL_INPUT_DIV_1 0b00 |

| #define PLL_CSI_CTRL_REG_PLL_INPUT_DIV_2 0b01 |

| #define PLL_CSI_CTRL_REG_PLL_INPUT_DIV_4 0b10 |

| #define PLL_CSI_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK (0x00000006) |

| #define PLL_CSI_CTRL_REG_PLL_INPUT_DIV_OFFSET 1 |

| #define PLL_CSI_CTRL_REG_PLL_LDO_EN_CLEAR_MASK (0x40000000) |

| #define PLL_CSI_CTRL_REG_PLL_LDO_EN_DISABLE 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_LDO_EN_ENABLE 0b1 |

| #define PLL_CSI_CTRL_REG_PLL_LDO_EN_OFFSET 30 |

| #define PLL_CSI_CTRL_REG_PLL_LOCK_MDSEL_23_27_CLOCK_CYCLES 0b1 |

| #define PLL_CSI_CTRL_REG_PLL_LOCK_MDSEL_24_26_CLOCK_CYCLES 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_LOCK_MDSEL_CLEAR_MASK (0x00000020) |

| #define PLL_CSI_CTRL_REG_PLL_LOCK_MDSEL_OFFSET 5 |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_DIV2_CLEAR_MASK (0x00000001) |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_DIV2_OFFSET 0 |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_GATE_CLEAR_MASK (0x08000000) |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_GATE_DISABLE 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_GATE_ENABLE 0b1 |

| #define PLL_CSI_CTRL_REG_PLL_OUTPUT_GATE_OFFSET 27 |

| #define PLL_CSI_CTRL_REG_PLL_SDM_EN_CLEAR_MASK (0x01000000) |

| #define PLL_CSI_CTRL_REG_PLL_SDM_EN_DISABLE 0b0 |

| #define PLL_CSI_CTRL_REG_PLL_SDM_EN_ENABLE 0b1 |

| #define PLL_CSI_CTRL_REG_PLL_SDM_EN_OFFSET 24 |

| #define PLL_CSI_CTRL_REG_PLL_UNLOCK_MDSEL_20_30_CLOCK_CYCLES 0b10 |

| #define PLL_CSI_CTRL_REG_PLL_UNLOCK_MDSEL_21_29_CLOCK_CYCLES 0b00 |

| #define PLL_CSI_CTRL_REG_PLL_UNLOCK_MDSEL_22_28_CLOCK_CYCLES 0b01 |

| #define PLL_CSI_CTRL_REG_PLL_UNLOCK_MDSEL_CLEAR_MASK (0x000000c0) |

| #define PLL_CSI_CTRL_REG_PLL_UNLOCK_MDSEL_OFFSET 6 |

| #define PLL_CSI_PAT0_CTRL_REG 0x00000148 |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_31_5KHZ 0b00 |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_32_5KHZ 0b10 |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_32KHZ 0b01 |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_33KHZ 0b11 |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_CLEAR_MASK (0x00060000) |

| #define PLL_CSI_PAT0_CTRL_REG_FREQ_OFFSET 17 |

| #define PLL_CSI_PAT0_CTRL_REG_SDM_CLK_SEL_10MHZ 0b10 |

| #define PLL_CSI_PAT0_CTRL_REG_SDM_CLK_SEL_20MHZ 0b01 |

| #define PLL_CSI_PAT0_CTRL_REG_SDM_CLK_SEL_40MHZ 0b00 |

| #define PLL_CSI_PAT0_CTRL_REG_SDM_CLK_SEL_CLEAR_MASK (0x00180000) |

| #define PLL_CSI_PAT0_CTRL_REG_SDM_CLK_SEL_OFFSET 19 |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_CLEAR_MASK (0xc0000000) |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_0 0b00 |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_DC_1 0b01 |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_OFFSET 30 |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_1BIT 0b10 |

| #define PLL_CSI_PAT0_CTRL_REG_SPR_FREQ_MODE_TRIANGULAR_NBIT 0b11 |

| #define PLL_CSI_PAT0_CTRL_REG_WAVE_BOT_CLEAR_MASK (0x0001ffff) |

| #define PLL_CSI_PAT0_CTRL_REG_WAVE_BOT_OFFSET 0 |

| #define PLL_CSI_PAT0_CTRL_REG_WAVE_STEP_CLEAR_MASK (0x3fe00000) |

| #define PLL_CSI_PAT0_CTRL_REG_WAVE_STEP_OFFSET 21 |

| #define PLL_CSI_PAT1_CTRL_REG 0x0000014c |

| #define PLL_CSI_PAT1_CTRL_REG_DITHER_EN_CLEAR_MASK (0x01000000) |

| #define PLL_CSI_PAT1_CTRL_REG_DITHER_EN_OFFSET 24 |

| #define PLL_CSI_PAT1_CTRL_REG_FRAC_EN_CLEAR_MASK (0x00100000) |

| #define PLL_CSI_PAT1_CTRL_REG_FRAC_EN_OFFSET 20 |

| #define PLL_CSI_PAT1_CTRL_REG_FRAC_IN_CLEAR_MASK (0x0001ffff) |

| #define PLL_CSI_PAT1_CTRL_REG_FRAC_IN_OFFSET 0 |

| #define PLL_CSI_PAT1_CTRL_REG_SIG_DELT_PAT_EN_CLEAR_MASK (0x80000000) |

| #define PLL_CSI_PAT1_CTRL_REG_SIG_DELT_PAT_EN_OFFSET 31 |

| #define PLL_D_MASK (PLL_CPU_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK) |

| #define PLL_D_OFFSET (PLL_CPU_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK) |

| #define PLL_DDR_BIAS_REG 0x00000380 |

| #define PLL_DDR_BIAS_REG_PLL_CP_CLEAR_MASK (0x001f0000) |

| #define PLL_DDR_BIAS_REG_PLL_CP_OFFSET 16 |

| #define PLL_DDR_CTRL_REG 0x00000080 |

| #define PLL_DDR_CTRL_REG_LOCK_CLEAR_MASK (0x10000000) |

| #define PLL_DDR_CTRL_REG_LOCK_ENABLE_CLEAR_MASK (0x20000000) |

| #define PLL_DDR_CTRL_REG_LOCK_ENABLE_DISABLE 0b0 |

| #define PLL_DDR_CTRL_REG_LOCK_ENABLE_ENABLE 0b1 |

| #define PLL_DDR_CTRL_REG_LOCK_ENABLE_OFFSET 29 |

| #define PLL_DDR_CTRL_REG_LOCK_LOCKED__IT_INDICATES_THAT_THE_PLL_HAS_BEEN_STABLE 0b1 |

| #define PLL_DDR_CTRL_REG_LOCK_OFFSET 28 |

| #define PLL_DDR_CTRL_REG_LOCK_UNLOCKED 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_EN_CLEAR_MASK (0x80000000) |

| #define PLL_DDR_CTRL_REG_PLL_EN_DISABLE 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_EN_ENABLE 0b1 |

| #define PLL_DDR_CTRL_REG_PLL_EN_OFFSET 31 |

| #define PLL_DDR_CTRL_REG_PLL_INPUT_DIV_1 0b00 |

| #define PLL_DDR_CTRL_REG_PLL_INPUT_DIV_2 0b01 |

| #define PLL_DDR_CTRL_REG_PLL_INPUT_DIV_4 0b10 |

| #define PLL_DDR_CTRL_REG_PLL_INPUT_DIV_CLEAR_MASK (0x00000006) |

| #define PLL_DDR_CTRL_REG_PLL_INPUT_DIV_OFFSET 1 |

| #define PLL_DDR_CTRL_REG_PLL_LDO_EN_CLEAR_MASK (0x40000000) |

| #define PLL_DDR_CTRL_REG_PLL_LDO_EN_DISABLE 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_LDO_EN_ENABLE 0b1 |

| #define PLL_DDR_CTRL_REG_PLL_LDO_EN_OFFSET 30 |

| #define PLL_DDR_CTRL_REG_PLL_LOCK_MDSEL_23_27_CLOCK_CYCLES 0b1 |

| #define PLL_DDR_CTRL_REG_PLL_LOCK_MDSEL_24_26_CLOCK_CYCLES 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_LOCK_MDSEL_CLEAR_MASK (0x00000020) |

| #define PLL_DDR_CTRL_REG_PLL_LOCK_MDSEL_OFFSET 5 |

| #define PLL_DDR_CTRL_REG_PLL_N_CLEAR_MASK (0x0000ff00) |

| #define PLL_DDR_CTRL_REG_PLL_N_OFFSET 8 |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_DIV2_CLEAR_MASK (0x00000001) |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_DIV2_OFFSET 0 |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_GATE_CLEAR_MASK (0x08000000) |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_GATE_DISABLE 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_GATE_ENABLE 0b1 |

| #define PLL_DDR_CTRL_REG_PLL_OUTPUT_GATE_OFFSET 27 |

| #define PLL_DDR_CTRL_REG_PLL_SDM_EN_CLEAR_MASK (0x01000000) |

| #define PLL_DDR_CTRL_REG_PLL_SDM_EN_DISABLE 0b0 |

| #define PLL_DDR_CTRL_REG_PLL_SDM_EN_ENABLE 0b1 |

| #define PLL_DDR_CTRL_REG_PLL_SDM_EN_OFFSET 24 |

| #define PLL_DDR_CTRL_REG_PLL_UNLOCK_MDSEL_20_30_CLOCK_CYCLES 0b10 |

| #define PLL_DDR_CTRL_REG_PLL_UNLOCK_MDSEL_21_29_CLOCK_CYCLES 0b00 |

| #define PLL_DDR_CTRL_REG_PLL_UNLOCK_MDSEL_22_28_CLOCK_CYCLES 0b01 |

| #define PLL_DDR_CTRL_REG_PLL_UNLOCK_MDSEL_CLEAR_MASK (0x000000c0) |

| #define PLL_DDR_CTRL_REG_PLL_UNLOCK_MDSEL_OFFSET 6 |

| #define PLL_DDR_PAT0_CTRL_REG 0x00000180 |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_31_5KHZ 0b00 |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_32_5KHZ 0b10 |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_32KHZ 0b01 |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_33KHZ 0b11 |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_CLEAR_MASK (0x00060000) |

| #define PLL_DDR_PAT0_CTRL_REG_FREQ_OFFSET 17 |

| #define PLL_DDR_PAT0_CTRL_REG_SDM_CLK_SEL_10MHZ 0b10 |

| #define PLL_DDR_PAT0_CTRL_REG_SDM_CLK_SEL_20MHZ 0b01 |