|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

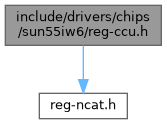

#include <reg-ncat.h>

Go to the source code of this file.

| #define AHB_CLK_REG 0x00000500 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define AHB_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define AHB_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define AHB_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define AHB_CLK_REG_CLK_SRC_SEL_PERI0_600M_BUS 0b11 |

| #define AHB_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define AHB_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AHB_GATE_EN_REG 0x000005c0 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_CLEAR_MASK 0x80000000 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_DISABLE_AUTO_CLOCK_GATE 0b0 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_ENABLE_AUTO_CLOCK_GATE 0b1 |

| #define AHB_GATE_EN_REG_AHB_MONITOR_EN_OFFSET 31 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_CLEAR_MASK 0x10000000 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_CPUS_HCLK_GATE_SW_CFG_OFFSET 28 |

| #define AHB_GATE_EN_REG_GMAC0_AHB_GATE_SW_CFG_CLEAR_MASK 0x00002000 |

| #define AHB_GATE_EN_REG_GMAC0_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_GMAC0_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_GMAC0_AHB_GATE_SW_CFG_OFFSET 13 |

| #define AHB_GATE_EN_REG_GMAC1_AHB_GATE_SW_CFG_CLEAR_MASK 0x00004000 |

| #define AHB_GATE_EN_REG_GMAC1_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_GMAC1_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_GMAC1_AHB_GATE_SW_CFG_OFFSET 14 |

| #define AHB_GATE_EN_REG_MCU_SYS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00001000 |

| #define AHB_GATE_EN_REG_MCU_SYS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_MCU_SYS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_MCU_SYS_AHB_GATE_SW_CFG_OFFSET 12 |

| #define AHB_GATE_EN_REG_NPU_AHB_GATE_SW_CFG_CLEAR_MASK 0x00008000 |

| #define AHB_GATE_EN_REG_NPU_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_NPU_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_NPU_AHB_GATE_SW_CFG_OFFSET 15 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_CLEAR_MASK 0x20000000 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_DISABLE_AUTO_CLOCK_GATE 0b0 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_ENABLE_AUTO_CLOCK_GATE 0b1 |

| #define AHB_GATE_EN_REG_SD_MONITOR_EN_OFFSET 29 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000020 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC0_AHB_GATE_SW_CFG_OFFSET 5 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC0_MBUS_AHB_GATE_SW_CFG_OFFSET 17 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000040 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC1_AHB_GATE_SW_CFG_OFFSET 6 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC1_MBUS_AHB_GATE_SW_CFG_OFFSET 18 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000080 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC2_AHB_GATE_SW_CFG_OFFSET 7 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00080000 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SMHC2_MBUS_AHB_GATE_SW_CFG_OFFSET 19 |

| #define AHB_GATE_EN_REG_SPIF_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00400000 |

| #define AHB_GATE_EN_REG_SPIF_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_SPIF_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_SPIF_MBUS_AHB_GATE_SW_CFG_OFFSET 22 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000010 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_USB_AHB_GATE_SW_CFG_OFFSET 4 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00010000 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_USB_MBUS_AHB_GATE_SW_CFG_OFFSET 16 |

| #define AHB_GATE_EN_REG_USB_SYS_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000800 |

| #define AHB_GATE_EN_REG_USB_SYS_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_USB_SYS_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_USB_SYS_AHB_GATE_SW_CFG_OFFSET 11 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000002 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VE_AHB_GATE_SW_CFG_OFFSET 1 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000004 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VID_IN_AHB_GATE_SW_CFG_OFFSET 2 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_CLEAR_MASK 0x00000008 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_DISABLE 0b0 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_ENABLE 0b1 |

| #define AHB_GATE_EN_REG_VID_OUT_AHB_GATE_SW_CFG_OFFSET 3 |

| #define APB0_CLK_REG 0x00000510 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define APB0_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define APB0_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define APB0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB0_CLK_REG_CLK_SRC_SEL_PERI0_600M_BUS 0b11 |

| #define APB0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define APB0_CLK_REG_FACTOR_N_CLEAR_MASK 0x00000300 |

| #define APB0_CLK_REG_FACTOR_N_OFFSET 8 |

| #define APB1_CLK_REG 0x00000518 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b10 |

| #define APB1_CLK_REG_CLK_SRC_SEL_CLK32K 0b01 |

| #define APB1_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define APB1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB1_CLK_REG_CLK_SRC_SEL_PERI0_600M_BUS 0b11 |

| #define APB1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define APB_UART_CLK_REG 0x00000538 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b010 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_CLK32K 0b001 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_PERI0_480M_BUS 0b100 |

| #define APB_UART_CLK_REG_CLK_SRC_SEL_PERI0_600M_BUS 0b011 |

| #define APB_UART_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define APB_UART_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AUDIO_CODEC_BGR_REG 0x000012ec |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_CLEAR_MASK 0x00000001 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_MASK 0b0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_OFFSET 0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_GATING_PASS 0b1 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_ASSERT 0b0 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_CLEAR_MASK 0x00010000 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_DE_ASSERT 0b1 |

| #define AUDIO_CODEC_BGR_REG_AUDIO_CODEC_RST_OFFSET 16 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG 0x000012e0 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b0 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b1 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_FACTOR_M_OFFSET 0 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_SCLK_GATING_CLEAR_MASK 0x80000000 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_SCLK_GATING_CLOCK_IS_OFF 0b0 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_SCLK_GATING_CLOCK_IS_ON 0b1 |

| #define AUDIO_CODEC_DAC_1X_CLK_REG_SCLK_GATING_OFFSET 31 |

| #define BUS_CLK_DBG_REG 0x00001f50 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_1_B0 0b111 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_AHB_CLOCK 0b000 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_APB0_CLOCK 0b001 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_APB1_CLOCK 0b010 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_APB_UART_CLOCK 0b011 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_CLEAR_MASK 0x00000007 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_DDR_CLK 0b110 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_MBUS_CLOCK 0b100 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_NSI_CLOCK 0b101 |

| #define BUS_CLK_DBG_REG_BUS_CLK_DBG_SEL_OFFSET 0 |

| #define CCU_APB1_CFG_GREG (SUNXI_CCU_BASE + APB1_CLK_REG) |

| #define CCU_APB_CFG_GREG (SUNXI_CCU_BASE + APB0_CLK_REG) |

| #define CCU_CE_BGR_REG (SUNXI_CCU_BASE + CE_BGR_REG) |

| #define CCU_CE_CLK_REG (SUNXI_CCU_BASE + CE_CLK_REG) |

| #define CCU_DMA_BGR_REG (SUNXI_CCU_BASE + DMA0_BGR_REG) |

| #define CCU_FAN_GATE_REG 0x00001f30 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLEAR_MASK 0x00000002 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK12M_EN_OFFSET 1 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLEAR_MASK 0x00000004 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK16M_EN_OFFSET 2 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLEAR_MASK 0x00000001 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK24M_EN_OFFSET 0 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLEAR_MASK 0x00000008 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK25M_EN_OFFSET 3 |

| #define CCU_FAN_GATE_REG_CLK50M_EN_CLEAR_MASK 0x00000010 |

| #define CCU_FAN_GATE_REG_CLK50M_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_GATE_REG_CLK50M_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_GATE_REG_CLK50M_EN_OFFSET 4 |

| #define CCU_FAN_REG 0x00001f3c |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLEAR_MASK 0x00200000 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT0_EN_OFFSET 21 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLEAR_MASK 0x00000007 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK16M_FROM_PERI0_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK25M_FROM_PERI0_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_CLK50M_FROM_PERI0_150M_3 0b111 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_OFFSET 0 |

| #define CCU_FAN_REG_CLK_FANOUT0_SEL_PCLK 0b110 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLEAR_MASK 0x00400000 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT1_EN_OFFSET 22 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLEAR_MASK 0x00000038 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK16M_FROM_PERI0_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK25M_FROM_PERI0_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_CLK50M_FROM_PERI0_150M_3 0b111 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_OFFSET 3 |

| #define CCU_FAN_REG_CLK_FANOUT1_SEL_PCLK 0b110 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLEAR_MASK 0x00800000 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLOCK_IS_OFF 0b0 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_CLOCK_IS_ON 0b1 |

| #define CCU_FAN_REG_CLK_FANOUT2_EN_OFFSET 23 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLEAR_MASK 0x000001c0 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK12M_FROM_DCXO_2 0b001 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK16M_FROM_PERI0_160M_10 0b010 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK24M_FROM_DCXO 0b011 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK25M_FROM_PERI0_150M_6 0b100 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK27M 0b101 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK32K_FANOUT_FROM_SYSRTC 0b000 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_CLK50M_FROM_PERI0_150M_3 0b111 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_OFFSET 6 |

| #define CCU_FAN_REG_CLK_FANOUT2_SEL_PCLK 0b110 |

| #define CCU_GPADC_BGR_REG (SUNXI_CCU_BASE + GPADC1_BGR_REG) |

| #define CCU_GPADC_CLK_REG (SUNXI_CCU_BASE + GPADC1_CLK_REG) |

| #define CCU_LRADC_BGR_REG (SUNXI_CCU_BASE + LRADC_BGR_REG) |

| #define CCU_MBUS_CFG_REG (SUNXI_CCU_BASE + MBUS_CLK_REG) |

| #define CCU_MBUS_MST_CLK_GATING_REG (SUNXI_CCU_BASE + MBUS_MAT_CLK_GATING_REG) |

| #define CCU_NSI_BGR_REG (SUNXI_CCU_BASE + NSI_BGR_REG) |

| #define CCU_NSI_CLK_GREG (SUNXI_CCU_BASE + NSI_CLK_REG) |

| #define CCU_REG_DSU_CLK (SUNXI_CPU_PLL_CFG_BASE + 0x4c) |

| #define CCU_REG_PLL_C0_CPUX (SUNXI_CPU_PLL_CFG_BASE + 0x4) |

| #define CCU_REG_PLL_C0_DSU (SUNXI_CPU_PLL_CFG_BASE + 0x8) |

| #define CCU_SDMMC0_CLK_REG (SUNXI_CCU_BASE + SMHC0_CLK_REG) |

| #define CCU_SDMMC1_CLK_REG (SUNXI_CCU_BASE + SMHC1_CLK_REG) |

| #define CCU_SDMMC2_CLK_REG (SUNXI_CCU_BASE + SMHC2_CLK_REG) |

| #define CCU_SEC_SWITCH_REG 0x00001f00 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_CLEAR_MASK 0x00000002 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_OFFSET 1 |

| #define CCU_SEC_SWITCH_REG_BUS_SEC_SECURE 0b0 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_CLEAR_MASK 0x00000004 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_OFFSET 2 |

| #define CCU_SEC_SWITCH_REG_MBUS_SEC_SECURE 0b0 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_CLEAR_MASK 0x00000001 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_NON_SECURE 0b1 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_OFFSET 0 |

| #define CCU_SEC_SWITCH_REG_PLL_SEC_SECURE 0b0 |

| #define CCU_SMHC0_BGR_REG (SUNXI_CCU_BASE + SMHC0_BGR_REG) |

| #define CCU_UART_BGR_REG (SUNXI_CCU_BASE + UART0_BGR_REG) |

| #define CCU_VERSION_REG 0x00001ff0 |

| #define CCU_VERSION_REG_CCU_MAIN_VERSION_CLEAR_MASK 0xffff0000 |

| #define CCU_VERSION_REG_CCU_MAIN_VERSION_OFFSET 16 |

| #define CCU_VERSION_REG_CCU_SUB_VERSION_CLEAR_MASK 0x0000ffff |

| #define CCU_VERSION_REG_CCU_SUB_VERSION_OFFSET 0 |

| #define CE_BGR_REG 0x00000ac4 |

| #define CE_BGR_REG_CE_GATING_CLEAR_MASK 0x00000001 |

| #define CE_BGR_REG_CE_GATING_MASK 0b0 |

| #define CE_BGR_REG_CE_GATING_OFFSET 0 |

| #define CE_BGR_REG_CE_GATING_SECURE_DEBUG 0b1 |

| #define CE_BGR_REG_CE_RST_ASSERT 0b0 |

| #define CE_BGR_REG_CE_RST_CLEAR_MASK 0x00010000 |

| #define CE_BGR_REG_CE_RST_OFFSET 16 |

| #define CE_BGR_REG_CE_RST_SECURE_DEBUG 0b1 |

| #define CE_BGR_REG_CE_SYS_GATING_CLEAR_MASK 0x00000002 |

| #define CE_BGR_REG_CE_SYS_GATING_MASK 0b0 |

| #define CE_BGR_REG_CE_SYS_GATING_OFFSET 1 |

| #define CE_BGR_REG_CE_SYS_GATING_SECURE_DEBUG 0b1 |

| #define CE_BGR_REG_CE_SYS_RST_ASSERT 0b0 |

| #define CE_BGR_REG_CE_SYS_RST_CLEAR_MASK 0x00020000 |

| #define CE_BGR_REG_CE_SYS_RST_OFFSET 17 |

| #define CE_BGR_REG_CE_SYS_RST_SECURE_DEBUG 0b1 |

| #define CE_CLK_DIV_RATION_M (2) |

| #define CE_CLK_DIV_RATION_M_BIT CE_CLK_REG_FACTOR_M_OFFSET |

| #define CE_CLK_DIV_RATION_M_MASK CE_CLK_REG_FACTOR_M_CLEAR_MASK |

| #define CE_CLK_REG 0x00000ac0 |

| #define CE_CLK_REG_CE_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CE_CLK_REG_CE_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CE_CLK_REG_CE_CLK_GATING_OFFSET 31 |

| #define CE_CLK_REG_CE_CLK_GATING_SECURE_DEBUG 0b1 |

| #define CE_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CE_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CE_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CE_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b010 |

| #define CE_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define CE_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CE_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CE_CLK_SRC CE_CLK_REG_CLK_SRC_SEL_PERI0_400M |

| #define CE_CLK_SRC_MASK (0x1) |

| #define CE_CLK_SRC_SEL_BIT CE_CLK_REG_CLK_SRC_SEL_OFFSET |

| #define CE_DEASSERT (1) |

| #define CE_GATING_BASE CCU_CE_BGR_REG |

| #define CE_GATING_BIT (0) |

| #define CE_GATING_PASS (1) |

| #define CE_RST_BIT CE_BGR_REG_CE_RST_OFFSET |

| #define CE_RST_REG_BASE CCU_CE_BGR_REG |

| #define CE_SCLK_ON (1) |

| #define CE_SCLK_ONOFF_BIT (31) |

| #define CE_SYS_GATING_BIT CE_BGR_REG_CE_GATING_MASK |

| #define CE_SYS_RST_BIT CE_BGR_REG_CE_SYS_RST_OFFSET |

| #define CLK24M_GATE_EN_REG 0x00001a00 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_CLEAR_MASK 0x00000008 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_DISABLE 0b0 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_ENABLE 0b1 |

| #define CLK24M_GATE_EN_REG_RES_DCAP_24M_GATE_EN_OFFSET 3 |

| #define CLK24M_GATE_EN_REG_USB20_24M_GATE_EN_CLEAR_MASK 0x00000001 |

| #define CLK24M_GATE_EN_REG_USB20_24M_GATE_EN_DISABLE 0b0 |

| #define CLK24M_GATE_EN_REG_USB20_24M_GATE_EN_ENABLE 0b1 |

| #define CLK24M_GATE_EN_REG_USB20_24M_GATE_EN_OFFSET 0 |

| #define CLK27M_FAN_REG 0x00001f34 |

| #define CLK27M_FAN_REG_CLK27M_DIV0_CLEAR_MASK 0x0000001f |

| #define CLK27M_FAN_REG_CLK27M_DIV0_OFFSET 0 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_CLEAR_MASK 0x00001f00 |

| #define CLK27M_FAN_REG_CLK27M_DIV1_OFFSET 8 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLEAR_MASK 0x80000000 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLOCK_IS_OFF 0b0 |

| #define CLK27M_FAN_REG_CLK27M_EN_CLOCK_IS_ON 0b1 |

| #define CLK27M_FAN_REG_CLK27M_EN_OFFSET 31 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_CLEAR_MASK 0x03000000 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_OFFSET 24 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_VIDEO0PLL4X 0b000 |

| #define CLK27M_FAN_REG_CLK27M_SCR_SEL_VIDEO1PLL4X 0b001 |

| #define CLK_FAN_REG 0x00001f38 |

| #define CLK_FAN_REG_PCLK_DIV1_CLEAR_MASK 0x000003e0 |

| #define CLK_FAN_REG_PCLK_DIV1_OFFSET 5 |

| #define CLK_FAN_REG_PCLK_DIV_CLEAR_MASK 0x0000001f |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLEAR_MASK 0x80000000 |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLOCK_IS_OFF 0b0 |

| #define CLK_FAN_REG_PCLK_DIV_EN_CLOCK_IS_ON 0b1 |

| #define CLK_FAN_REG_PCLK_DIV_EN_OFFSET 31 |

| #define CLK_FAN_REG_PCLK_DIV_OFFSET 0 |

| #define CM_NPU_CFG_REG 0x00001b1c |

| #define CM_NPU_CFG_REG_CM_NPU_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_NPU_CFG_REG_CM_NPU_MODULE_MODE_DISABLE 0b0 |

| #define CM_NPU_CFG_REG_CM_NPU_MODULE_MODE_ENABLE 0b1 |

| #define CM_NPU_CFG_REG_CM_NPU_MODULE_MODE_OFFSET 0 |

| #define CM_NPU_CFG_REG_CM_NPU_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_NPU_CFG_REG_CM_NPU_STATUS_OFFSET 16 |

| #define CM_NPU_CFG_REG_CM_NPU_STATUS_POWER_OFF 0b01 |

| #define CM_NPU_CFG_REG_CM_NPU_STATUS_POWER_ON 0b10 |

| #define CM_RV_CFG_REG 0x00001b40 |

| #define CM_RV_CFG_REG_CM_RV_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_RV_CFG_REG_CM_RV_MODULE_MODE_DISABLE 0b0 |

| #define CM_RV_CFG_REG_CM_RV_MODULE_MODE_ENABLE 0b1 |

| #define CM_RV_CFG_REG_CM_RV_MODULE_MODE_OFFSET 0 |

| #define CM_RV_CFG_REG_CM_RV_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_RV_CFG_REG_CM_RV_STATUS_OFFSET 16 |

| #define CM_RV_CFG_REG_CM_RV_STATUS_POWER_OFF 0b01 |

| #define CM_RV_CFG_REG_CM_RV_STATUS_POWER_ON 0b10 |

| #define CM_SERDES_CFG_REG 0x00001b28 |

| #define CM_SERDES_CFG_REG_CM_SERDES_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_SERDES_CFG_REG_CM_SERDES_MODULE_MODE_DISABLE 0b0 |

| #define CM_SERDES_CFG_REG_CM_SERDES_MODULE_MODE_ENABLE 0b1 |

| #define CM_SERDES_CFG_REG_CM_SERDES_MODULE_MODE_OFFSET 0 |

| #define CM_SERDES_CFG_REG_CM_SERDES_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_SERDES_CFG_REG_CM_SERDES_STATUS_OFFSET 16 |

| #define CM_SERDES_CFG_REG_CM_SERDES_STATUS_POWER_OFF 0b01 |

| #define CM_SERDES_CFG_REG_CM_SERDES_STATUS_POWER_ON 0b10 |

| #define CM_VE_CFG_REG 0x00001b10 |

| #define CM_VE_CFG_REG_CM_VE_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_VE_CFG_REG_CM_VE_MODULE_MODE_DISABLE 0b0 |

| #define CM_VE_CFG_REG_CM_VE_MODULE_MODE_ENABLE 0b1 |

| #define CM_VE_CFG_REG_CM_VE_MODULE_MODE_OFFSET 0 |

| #define CM_VE_CFG_REG_CM_VE_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_VE_CFG_REG_CM_VE_STATUS_OFFSET 16 |

| #define CM_VE_CFG_REG_CM_VE_STATUS_POWER_OFF 0b01 |

| #define CM_VE_CFG_REG_CM_VE_STATUS_POWER_ON 0b10 |

| #define CM_VI_CFG_REG 0x00001b00 |

| #define CM_VI_CFG_REG_CM_VI_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_VI_CFG_REG_CM_VI_MODULE_MODE_DISABLE 0b0 |

| #define CM_VI_CFG_REG_CM_VI_MODULE_MODE_ENABLE 0b1 |

| #define CM_VI_CFG_REG_CM_VI_MODULE_MODE_OFFSET 0 |

| #define CM_VI_CFG_REG_CM_VI_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_VI_CFG_REG_CM_VI_STATUS_OFFSET 16 |

| #define CM_VI_CFG_REG_CM_VI_STATUS_POWER_OFF 0b01 |

| #define CM_VI_CFG_REG_CM_VI_STATUS_POWER_ON 0b10 |

| #define CM_VO_CFG_REG 0x00001b34 |

| #define CM_VO_CFG_REG_CM_VO_MODULE_MODE_CLEAR_MASK 0x00000001 |

| #define CM_VO_CFG_REG_CM_VO_MODULE_MODE_DISABLE 0b0 |

| #define CM_VO_CFG_REG_CM_VO_MODULE_MODE_ENABLE 0b1 |

| #define CM_VO_CFG_REG_CM_VO_MODULE_MODE_OFFSET 0 |

| #define CM_VO_CFG_REG_CM_VO_STATUS_CLEAR_MASK 0x00030000 |

| #define CM_VO_CFG_REG_CM_VO_STATUS_OFFSET 16 |

| #define CM_VO_CFG_REG_CM_VO_STATUS_POWER_OFF 0b01 |

| #define CM_VO_CFG_REG_CM_VO_STATUS_POWER_ON 0b10 |

| #define CSI_BGR_REG 0x00001844 |

| #define CSI_BGR_REG_CSI_GATING_CLEAR_MASK 0x00000001 |

| #define CSI_BGR_REG_CSI_GATING_MASK 0b0 |

| #define CSI_BGR_REG_CSI_GATING_OFFSET 0 |

| #define CSI_BGR_REG_CSI_GATING_PASS 0b1 |

| #define CSI_BGR_REG_CSI_RST_ASSERT 0b0 |

| #define CSI_BGR_REG_CSI_RST_CLEAR_MASK 0x00010000 |

| #define CSI_BGR_REG_CSI_RST_DE_ASSERT 0b1 |

| #define CSI_BGR_REG_CSI_RST_OFFSET 16 |

| #define CSI_CLK_REG 0x00001840 |

| #define CSI_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b010 |

| #define CSI_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define CSI_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b000 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VEPLL 0b111 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b100 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b011 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b110 |

| #define CSI_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b101 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_CLK_REG_CSI_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_CLK_REG_CSI_CLK_GATING_OFFSET 31 |

| #define CSI_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER0_CLK_REG 0x00001800 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b100 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b011 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b010 |

| #define CSI_MASTER0_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b001 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER0_CLK_REG_CSI_MASTER0_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_CLEAR_MASK 0x00001f00 |

| #define CSI_MASTER0_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSI_MASTER1_CLK_REG 0x00001804 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b100 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b011 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b010 |

| #define CSI_MASTER1_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b001 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER1_CLK_REG_CSI_MASTER1_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_CLEAR_MASK 0x00001f00 |

| #define CSI_MASTER1_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSI_MASTER2_CLK_REG 0x00001808 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b100 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b011 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b010 |

| #define CSI_MASTER2_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b001 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER2_CLK_REG_CSI_MASTER2_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER2_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER2_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_CLEAR_MASK 0x00001f00 |

| #define CSI_MASTER2_CLK_REG_FACTOR_N_OFFSET 8 |

| #define CSI_MASTER3_CLK_REG 0x0000180c |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b100 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b011 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b010 |

| #define CSI_MASTER3_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b001 |

| #define CSI_MASTER3_CLK_REG_CSI_MASTER3_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define CSI_MASTER3_CLK_REG_CSI_MASTER3_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define CSI_MASTER3_CLK_REG_CSI_MASTER3_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define CSI_MASTER3_CLK_REG_CSI_MASTER3_CLK_GATING_OFFSET 31 |

| #define CSI_MASTER3_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define CSI_MASTER3_CLK_REG_FACTOR_M_OFFSET 0 |

| #define CSI_MASTER3_CLK_REG_FACTOR_N_CLEAR_MASK 0x00001f00 |

| #define CSI_MASTER3_CLK_REG_FACTOR_N_OFFSET 8 |

| #define DBGSYS_BGR_REG 0x000007a4 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_CLEAR_MASK 0x00000001 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_MASK 0b0 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_OFFSET 0 |

| #define DBGSYS_BGR_REG_DBGSYS_GATING_PASS 0b1 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_ASSERT 0b0 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_CLEAR_MASK 0x00010000 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_DE_ASSERT 0b1 |

| #define DBGSYS_BGR_REG_DBGSYS_RST_OFFSET 16 |

| #define DE0_BGR_REG 0x00000a04 |

| #define DE0_BGR_REG_DE0_GATING_CLEAR_MASK 0x00000001 |

| #define DE0_BGR_REG_DE0_GATING_MASK 0b0 |

| #define DE0_BGR_REG_DE0_GATING_OFFSET 0 |

| #define DE0_BGR_REG_DE0_GATING_PASS 0b1 |

| #define DE0_BGR_REG_DE0_RST_ASSERT 0b0 |

| #define DE0_BGR_REG_DE0_RST_CLEAR_MASK 0x00010000 |

| #define DE0_BGR_REG_DE0_RST_DE_ASSERT 0b1 |

| #define DE0_BGR_REG_DE0_RST_OFFSET 16 |

| #define DE0_CLK_REG 0x00000a00 |

| #define DE0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define DE0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define DE0_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b1 |

| #define DE0_CLK_REG_CLK_SRC_SEL_PERI0_600M 0b0 |

| #define DE0_CLK_REG_DE0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DE0_CLK_REG_DE0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DE0_CLK_REG_DE0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DE0_CLK_REG_DE0_CLK_GATING_OFFSET 31 |

| #define DE0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define DE0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define DE_SYS_BGR_REG 0x00000a74 |

| #define DE_SYS_BGR_REG_DE_SYS_RST_ASSERT 0b0 |

| #define DE_SYS_BGR_REG_DE_SYS_RST_CLEAR_MASK 0x00010000 |

| #define DE_SYS_BGR_REG_DE_SYS_RST_DE_ASSERT 0b1 |

| #define DE_SYS_BGR_REG_DE_SYS_RST_OFFSET 16 |

| #define DMA0_BGR_REG 0x00000704 |

| #define DMA0_BGR_REG_DMA0_GATING_CLEAR_MASK 0x00000001 |

| #define DMA0_BGR_REG_DMA0_GATING_MASK 0b0 |

| #define DMA0_BGR_REG_DMA0_GATING_OFFSET 0 |

| #define DMA0_BGR_REG_DMA0_GATING_PASS 0b1 |

| #define DMA0_BGR_REG_DMA0_RST_ASSERT 0b0 |

| #define DMA0_BGR_REG_DMA0_RST_CLEAR_MASK 0x00010000 |

| #define DMA0_BGR_REG_DMA0_RST_DE_ASSERT 0b1 |

| #define DMA0_BGR_REG_DMA0_RST_OFFSET 16 |

| #define DMA1_BGR_REG 0x0000070c |

| #define DMA1_BGR_REG_DMA1_GATING_CLEAR_MASK 0x00000001 |

| #define DMA1_BGR_REG_DMA1_GATING_MASK 0b0 |

| #define DMA1_BGR_REG_DMA1_GATING_OFFSET 0 |

| #define DMA1_BGR_REG_DMA1_GATING_PASS 0b1 |

| #define DMA1_BGR_REG_DMA1_RST_ASSERT 0b0 |

| #define DMA1_BGR_REG_DMA1_RST_CLEAR_MASK 0x00010000 |

| #define DMA1_BGR_REG_DMA1_RST_DE_ASSERT 0b1 |

| #define DMA1_BGR_REG_DMA1_RST_OFFSET 16 |

| #define DMIC_BGR_REG 0x000012cc |

| #define DMIC_BGR_REG_DMIC_GATING_CLEAR_MASK 0x00000001 |

| #define DMIC_BGR_REG_DMIC_GATING_MASK 0b0 |

| #define DMIC_BGR_REG_DMIC_GATING_OFFSET 0 |

| #define DMIC_BGR_REG_DMIC_GATING_PASS 0b1 |

| #define DMIC_BGR_REG_DMIC_RST_ASSERT 0b0 |

| #define DMIC_BGR_REG_DMIC_RST_CLEAR_MASK 0x00010000 |

| #define DMIC_BGR_REG_DMIC_RST_DE_ASSERT 0b1 |

| #define DMIC_BGR_REG_DMIC_RST_OFFSET 16 |

| #define DMIC_CLK_REG 0x000012c0 |

| #define DMIC_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b0 |

| #define DMIC_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b1 |

| #define DMIC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define DMIC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define DMIC_CLK_REG_DMIC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DMIC_CLK_REG_DMIC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DMIC_CLK_REG_DMIC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DMIC_CLK_REG_DMIC_CLK_GATING_OFFSET 31 |

| #define DMIC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define DMIC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define DPSS_BGR_REG 0x000016c4 |

| #define DPSS_BGR_REG_DPSS_GATING_CLEAR_MASK 0x00000001 |

| #define DPSS_BGR_REG_DPSS_GATING_MASK 0b0 |

| #define DPSS_BGR_REG_DPSS_GATING_OFFSET 0 |

| #define DPSS_BGR_REG_DPSS_GATING_PASS 0b1 |

| #define DPSS_BGR_REG_DPSS_RST_ASSERT 0b0 |

| #define DPSS_BGR_REG_DPSS_RST_CLEAR_MASK 0x00010000 |

| #define DPSS_BGR_REG_DPSS_RST_DE_ASSERT 0b1 |

| #define DPSS_BGR_REG_DPSS_RST_OFFSET 16 |

| #define DRAM_BGR_REG 0x00000c0c |

| #define DRAM_BGR_REG_DRAM_GATING_CLEAR_MASK 0x00000001 |

| #define DRAM_BGR_REG_DRAM_GATING_MASK 0b0 |

| #define DRAM_BGR_REG_DRAM_GATING_OFFSET 0 |

| #define DRAM_BGR_REG_DRAM_GATING_PASS 0b1 |

| #define DRAM_BGR_REG_DRAM_RST_ASSERT 0b0 |

| #define DRAM_BGR_REG_DRAM_RST_CLEAR_MASK 0x00010000 |

| #define DRAM_BGR_REG_DRAM_RST_DE_ASSERT 0b1 |

| #define DRAM_BGR_REG_DRAM_RST_OFFSET 16 |

| #define DRAM_CLK_REG 0x00000c00 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DRAM_CLK_REG_DRAM_CLK_GATING_OFFSET 31 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_CLEAR_MASK 0x07000000 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_DDRPLL 0b000 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_HOSC 0b101 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_NPUPLL 0b100 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_OFFSET 24 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI1_480M 0b011 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI1_600M 0b010 |

| #define DRAM_CLK_REG_DRAM_CLK_SEL_PERI1_800M 0b001 |

| #define DRAM_CLK_REG_DRAM_DIV1_CLEAR_MASK 0x0000001f |

| #define DRAM_CLK_REG_DRAM_DIV1_OFFSET 0 |

| #define DRAM_CLK_REG_DRAM_UPD_CLEAR_MASK 0x08000000 |

| #define DRAM_CLK_REG_DRAM_UPD_INVALID 0b0 |

| #define DRAM_CLK_REG_DRAM_UPD_OFFSET 27 |

| #define DRAM_CLK_REG_DRAM_UPD_VALID 0b1 |

| #define DSI0_BGR_REG 0x00001584 |

| #define DSI0_BGR_REG_DSI0_GATING_CLEAR_MASK 0x00000001 |

| #define DSI0_BGR_REG_DSI0_GATING_MASK 0b0 |

| #define DSI0_BGR_REG_DSI0_GATING_OFFSET 0 |

| #define DSI0_BGR_REG_DSI0_GATING_PASS 0b1 |

| #define DSI0_BGR_REG_DSI0_RST_ASSERT 0b0 |

| #define DSI0_BGR_REG_DSI0_RST_CLEAR_MASK 0x00010000 |

| #define DSI0_BGR_REG_DSI0_RST_DE_ASSERT 0b1 |

| #define DSI0_BGR_REG_DSI0_RST_OFFSET 16 |

| #define DSI0_CLK_REG 0x00001580 |

| #define DSI0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define DSI0_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define DSI0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define DSI0_CLK_REG_CLK_SRC_SEL_PERI0_150M 0b010 |

| #define DSI0_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b001 |

| #define DSI0_CLK_REG_DSI0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define DSI0_CLK_REG_DSI0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define DSI0_CLK_REG_DSI0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define DSI0_CLK_REG_DSI0_CLK_GATING_OFFSET 31 |

| #define DSI0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define DSI0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define G2D_BGR_REG 0x00000a44 |

| #define G2D_BGR_REG_G2D_GATING_CLEAR_MASK 0x00000001 |

| #define G2D_BGR_REG_G2D_GATING_MASK 0b0 |

| #define G2D_BGR_REG_G2D_GATING_OFFSET 0 |

| #define G2D_BGR_REG_G2D_GATING_PASS 0b1 |

| #define G2D_BGR_REG_G2D_RST_ASSERT 0b0 |

| #define G2D_BGR_REG_G2D_RST_CLEAR_MASK 0x00010000 |

| #define G2D_BGR_REG_G2D_RST_DE_ASSERT 0b1 |

| #define G2D_BGR_REG_G2D_RST_OFFSET 16 |

| #define G2D_CLK_REG 0x00000a40 |

| #define G2D_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define G2D_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define G2D_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b1 |

| #define G2D_CLK_REG_CLK_SRC_SEL_PERI0_600M 0b0 |

| #define G2D_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define G2D_CLK_REG_FACTOR_M_OFFSET 0 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define G2D_CLK_REG_G2D_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define G2D_CLK_REG_G2D_CLK_GATING_OFFSET 31 |

| #define GIC_CLK_REG 0x00000560 |

| #define GIC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define GIC_CLK_REG_CLK_SRC_SEL_CLK16M_RC 0b010 |

| #define GIC_CLK_REG_CLK_SRC_SEL_CLK32K 0b001 |

| #define GIC_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define GIC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GIC_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b101 |

| #define GIC_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b100 |

| #define GIC_CLK_REG_CLK_SRC_SEL_PERI0_600M 0b011 |

| #define GIC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GIC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GIC_CLK_REG_GIC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GIC_CLK_REG_GIC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GIC_CLK_REG_GIC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GIC_CLK_REG_GIC_CLK_GATING_OFFSET 31 |

| #define GMAC0_BGR_REG 0x0000140c |

| #define GMAC0_BGR_REG_GMAC0_AXI_RST_ASSERT 0b0 |

| #define GMAC0_BGR_REG_GMAC0_AXI_RST_CLEAR_MASK 0x00020000 |

| #define GMAC0_BGR_REG_GMAC0_AXI_RST_DE_ASSERT 0b1 |

| #define GMAC0_BGR_REG_GMAC0_AXI_RST_OFFSET 17 |

| #define GMAC0_BGR_REG_GMAC0_GATING_CLEAR_MASK 0x00000001 |

| #define GMAC0_BGR_REG_GMAC0_GATING_MASK 0b0 |

| #define GMAC0_BGR_REG_GMAC0_GATING_OFFSET 0 |

| #define GMAC0_BGR_REG_GMAC0_GATING_PASS 0b1 |

| #define GMAC0_BGR_REG_GMAC0_RST_ASSERT 0b0 |

| #define GMAC0_BGR_REG_GMAC0_RST_CLEAR_MASK 0x00010000 |

| #define GMAC0_BGR_REG_GMAC0_RST_DE_ASSERT 0b1 |

| #define GMAC0_BGR_REG_GMAC0_RST_OFFSET 16 |

| #define GMAC0_PHY_CLK_REG 0x00001400 |

| #define GMAC0_PHY_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GMAC0_PHY_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GMAC0_PHY_CLK_REG_GMAC0_PHY_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GMAC0_PHY_CLK_REG_GMAC0_PHY_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC0_PHY_CLK_REG_GMAC0_PHY_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC0_PHY_CLK_REG_GMAC0_PHY_CLK_GATING_OFFSET 31 |

| #define GMAC0_PTP_CLK_REG 0x00001404 |

| #define GMAC0_PTP_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define GMAC0_PTP_CLK_REG_CLK_SRC_SEL_HOSC 0b0 |

| #define GMAC0_PTP_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GMAC0_PTP_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b1 |

| #define GMAC0_PTP_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GMAC0_PTP_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GMAC0_PTP_CLK_REG_GMAC0_PTP_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GMAC0_PTP_CLK_REG_GMAC0_PTP_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC0_PTP_CLK_REG_GMAC0_PTP_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC0_PTP_CLK_REG_GMAC0_PTP_CLK_GATING_OFFSET 31 |

| #define GMAC1_BGR_REG 0x0000141c |

| #define GMAC1_BGR_REG_GMAC1_AXI_RST_ASSERT 0b0 |

| #define GMAC1_BGR_REG_GMAC1_AXI_RST_CLEAR_MASK 0x00020000 |

| #define GMAC1_BGR_REG_GMAC1_AXI_RST_DE_ASSERT 0b1 |

| #define GMAC1_BGR_REG_GMAC1_AXI_RST_OFFSET 17 |

| #define GMAC1_BGR_REG_GMAC1_GATING_CLEAR_MASK 0x00000001 |

| #define GMAC1_BGR_REG_GMAC1_GATING_MASKS 0b0 |

| #define GMAC1_BGR_REG_GMAC1_GATING_OFFSET 0 |

| #define GMAC1_BGR_REG_GMAC1_GATING_PASS 0b1 |

| #define GMAC1_BGR_REG_GMAC1_RST_ASSERT 0b0 |

| #define GMAC1_BGR_REG_GMAC1_RST_CLEAR_MASK 0x00010000 |

| #define GMAC1_BGR_REG_GMAC1_RST_DE_ASSERT 0b1 |

| #define GMAC1_BGR_REG_GMAC1_RST_OFFSET 16 |

| #define GMAC1_PHY_CLK_REG 0x00001410 |

| #define GMAC1_PHY_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GMAC1_PHY_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GMAC1_PHY_CLK_REG_GMAC1_PHY_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GMAC1_PHY_CLK_REG_GMAC1_PHY_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC1_PHY_CLK_REG_GMAC1_PHY_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC1_PHY_CLK_REG_GMAC1_PHY_CLK_GATING_OFFSET 31 |

| #define GMAC1_PTP_CLK_REG 0x00001414 |

| #define GMAC1_PTP_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define GMAC1_PTP_CLK_REG_CLK_SRC_SEL_HOSC 0b0 |

| #define GMAC1_PTP_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GMAC1_PTP_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b1 |

| #define GMAC1_PTP_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GMAC1_PTP_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GMAC1_PTP_CLK_REG_GMAC1_PTP_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GMAC1_PTP_CLK_REG_GMAC1_PTP_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GMAC1_PTP_CLK_REG_GMAC1_PTP_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GMAC1_PTP_CLK_REG_GMAC1_PTP_CLK_GATING_OFFSET 31 |

| #define GPADC0_BGR_REG 0x00000fc4 |

| #define GPADC0_BGR_REG_GPADC0_GATING_CLEAR_MASK 0x00000001 |

| #define GPADC0_BGR_REG_GPADC0_GATING_MASK 0b0 |

| #define GPADC0_BGR_REG_GPADC0_GATING_OFFSET 0 |

| #define GPADC0_BGR_REG_GPADC0_GATING_PASS 0b1 |

| #define GPADC0_BGR_REG_GPADC0_RST_ASSERT 0b0 |

| #define GPADC0_BGR_REG_GPADC0_RST_CLEAR_MASK 0x00010000 |

| #define GPADC0_BGR_REG_GPADC0_RST_DE_ASSERT 0b1 |

| #define GPADC0_BGR_REG_GPADC0_RST_OFFSET 16 |

| #define GPADC0_CLK_REG 0x00000fc0 |

| #define GPADC0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define GPADC0_CLK_REG_CLK_SRC_SEL_CLK48M 0b001 |

| #define GPADC0_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define GPADC0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GPADC0_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b010 |

| #define GPADC0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GPADC0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GPADC0_CLK_REG_GPADC0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GPADC0_CLK_REG_GPADC0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GPADC0_CLK_REG_GPADC0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GPADC0_CLK_REG_GPADC0_CLK_GATING_OFFSET 31 |

| #define GPADC1_BGR_REG 0x00000fcc |

| #define GPADC1_BGR_REG_GPADC1_GATING_CLEAR_MASK 0x00000001 |

| #define GPADC1_BGR_REG_GPADC1_GATING_MASK 0b0 |

| #define GPADC1_BGR_REG_GPADC1_GATING_OFFSET 0 |

| #define GPADC1_BGR_REG_GPADC1_GATING_PASS 0b1 |

| #define GPADC1_BGR_REG_GPADC1_RST_ASSERT 0b0 |

| #define GPADC1_BGR_REG_GPADC1_RST_CLEAR_MASK 0x00010000 |

| #define GPADC1_BGR_REG_GPADC1_RST_DE_ASSERT 0b1 |

| #define GPADC1_BGR_REG_GPADC1_RST_OFFSET 16 |

| #define GPADC1_CLK_REG 0x00000fc8 |

| #define GPADC1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define GPADC1_CLK_REG_CLK_SRC_SEL_CLK48M 0b001 |

| #define GPADC1_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define GPADC1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GPADC1_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b010 |

| #define GPADC1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GPADC1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GPADC1_CLK_REG_GPADC1_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GPADC1_CLK_REG_GPADC1_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GPADC1_CLK_REG_GPADC1_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GPADC1_CLK_REG_GPADC1_CLK_GATING_OFFSET 31 |

| #define GPADC2_BGR_REG 0x00000fd4 |

| #define GPADC2_BGR_REG_GPADC2_GATING_CLEAR_MASK 0x00000001 |

| #define GPADC2_BGR_REG_GPADC2_GATING_MASK 0b0 |

| #define GPADC2_BGR_REG_GPADC2_GATING_OFFSET 0 |

| #define GPADC2_BGR_REG_GPADC2_GATING_PASS 0b1 |

| #define GPADC2_BGR_REG_GPADC2_RST_ASSERT 0b0 |

| #define GPADC2_BGR_REG_GPADC2_RST_CLEAR_MASK 0x00010000 |

| #define GPADC2_BGR_REG_GPADC2_RST_DE_ASSERT 0b1 |

| #define GPADC2_BGR_REG_GPADC2_RST_OFFSET 16 |

| #define GPADC2_CLK_REG 0x00000fd0 |

| #define GPADC2_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define GPADC2_CLK_REG_CLK_SRC_SEL_CLK48M 0b001 |

| #define GPADC2_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define GPADC2_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GPADC2_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b010 |

| #define GPADC2_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GPADC2_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GPADC2_CLK_REG_GPADC2_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GPADC2_CLK_REG_GPADC2_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GPADC2_CLK_REG_GPADC2_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GPADC2_CLK_REG_GPADC2_CLK_GATING_OFFSET 31 |

| #define GPADC3_BGR_REG 0x00000fdc |

| #define GPADC3_BGR_REG_GPADC3_GATING_CLEAR_MASK 0x00000001 |

| #define GPADC3_BGR_REG_GPADC3_GATING_MASK 0b0 |

| #define GPADC3_BGR_REG_GPADC3_GATING_OFFSET 0 |

| #define GPADC3_BGR_REG_GPADC3_GATING_PASS 0b1 |

| #define GPADC3_BGR_REG_GPADC3_RST_ASSERT 0b0 |

| #define GPADC3_BGR_REG_GPADC3_RST_CLEAR_MASK 0x00010000 |

| #define GPADC3_BGR_REG_GPADC3_RST_DE_ASSERT 0b1 |

| #define GPADC3_BGR_REG_GPADC3_RST_OFFSET 16 |

| #define GPADC3_CLK_REG 0x00000fd8 |

| #define GPADC3_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define GPADC3_CLK_REG_CLK_SRC_SEL_CLK48M 0b001 |

| #define GPADC3_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define GPADC3_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define GPADC3_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b010 |

| #define GPADC3_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define GPADC3_CLK_REG_FACTOR_M_OFFSET 0 |

| #define GPADC3_CLK_REG_GPADC3_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define GPADC3_CLK_REG_GPADC3_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define GPADC3_CLK_REG_GPADC3_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define GPADC3_CLK_REG_GPADC3_CLK_GATING_OFFSET 31 |

| #define I2SPCM0_BGR_REG 0x0000120c |

| #define I2SPCM0_BGR_REG_I2SPCM0_GATING_CLEAR_MASK 0x00000001 |

| #define I2SPCM0_BGR_REG_I2SPCM0_GATING_MASK 0b0 |

| #define I2SPCM0_BGR_REG_I2SPCM0_GATING_OFFSET 0 |

| #define I2SPCM0_BGR_REG_I2SPCM0_GATING_PASS 0b1 |

| #define I2SPCM0_BGR_REG_I2SPCM0_RST_ASSERT 0b0 |

| #define I2SPCM0_BGR_REG_I2SPCM0_RST_CLEAR_MASK 0x00010000 |

| #define I2SPCM0_BGR_REG_I2SPCM0_RST_DE_ASSERT 0b1 |

| #define I2SPCM0_BGR_REG_I2SPCM0_RST_OFFSET 16 |

| #define I2SPCM0_CLK_REG 0x00001200 |

| #define I2SPCM0_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b000 |

| #define I2SPCM0_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b001 |

| #define I2SPCM0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define I2SPCM0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define I2SPCM0_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b010 |

| #define I2SPCM0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define I2SPCM0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define I2SPCM0_CLK_REG_SCLK_GATING_CLEAR_MASK 0x80000000 |

| #define I2SPCM0_CLK_REG_SCLK_GATING_CLOCK_IS_OFF 0b0 |

| #define I2SPCM0_CLK_REG_SCLK_GATING_CLOCK_IS_ON 0b1 |

| #define I2SPCM0_CLK_REG_SCLK_GATING_OFFSET 31 |

| #define I2SPCM1_BGR_REG 0x0000121c |

| #define I2SPCM1_BGR_REG_I2SPCM1_GATING_CLEAR_MASK 0x00000001 |

| #define I2SPCM1_BGR_REG_I2SPCM1_GATING_MASK 0b0 |

| #define I2SPCM1_BGR_REG_I2SPCM1_GATING_OFFSET 0 |

| #define I2SPCM1_BGR_REG_I2SPCM1_GATING_PASS 0b1 |

| #define I2SPCM1_BGR_REG_I2SPCM1_RST_ASSERT 0b0 |

| #define I2SPCM1_BGR_REG_I2SPCM1_RST_CLEAR_MASK 0x00010000 |

| #define I2SPCM1_BGR_REG_I2SPCM1_RST_DE_ASSERT 0b1 |

| #define I2SPCM1_BGR_REG_I2SPCM1_RST_OFFSET 16 |

| #define I2SPCM1_CLK_REG 0x00001210 |

| #define I2SPCM1_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b000 |

| #define I2SPCM1_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b001 |

| #define I2SPCM1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define I2SPCM1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define I2SPCM1_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b010 |

| #define I2SPCM1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define I2SPCM1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define I2SPCM1_CLK_REG_SCLK_GATING_CLEAR_MASK 0x80000000 |

| #define I2SPCM1_CLK_REG_SCLK_GATING_CLOCK_IS_OFF 0b0 |

| #define I2SPCM1_CLK_REG_SCLK_GATING_CLOCK_IS_ON 0b1 |

| #define I2SPCM1_CLK_REG_SCLK_GATING_OFFSET 31 |

| #define I2SPCM2_BGR_REG 0x0000122c |

| #define I2SPCM2_BGR_REG_I2SPCM2_GATING_CLEAR_MASK 0x00000001 |

| #define I2SPCM2_BGR_REG_I2SPCM2_GATING_MASK 0b0 |

| #define I2SPCM2_BGR_REG_I2SPCM2_GATING_OFFSET 0 |

| #define I2SPCM2_BGR_REG_I2SPCM2_GATING_PASS 0b1 |

| #define I2SPCM2_BGR_REG_I2SPCM2_RST_ASSERT 0b0 |

| #define I2SPCM2_BGR_REG_I2SPCM2_RST_CLEAR_MASK 0x00010000 |

| #define I2SPCM2_BGR_REG_I2SPCM2_RST_DE_ASSERT 0b1 |

| #define I2SPCM2_BGR_REG_I2SPCM2_RST_OFFSET 16 |

| #define I2SPCM2_CLK_REG 0x00001220 |

| #define I2SPCM2_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b000 |

| #define I2SPCM2_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b001 |

| #define I2SPCM2_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define I2SPCM2_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define I2SPCM2_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b010 |

| #define I2SPCM2_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define I2SPCM2_CLK_REG_FACTOR_M_OFFSET 0 |

| #define I2SPCM2_CLK_REG_SCLK_GATING_CLEAR_MASK 0x80000000 |

| #define I2SPCM2_CLK_REG_SCLK_GATING_CLOCK_IS_OFF 0b0 |

| #define I2SPCM2_CLK_REG_SCLK_GATING_CLOCK_IS_ON 0b1 |

| #define I2SPCM2_CLK_REG_SCLK_GATING_OFFSET 31 |

| #define I2SPCM3_BGR_REG 0x0000123c |

| #define I2SPCM3_BGR_REG_I2SPCM3_GATING_CLEAR_MASK 0x00000001 |

| #define I2SPCM3_BGR_REG_I2SPCM3_GATING_MASK 0b0 |

| #define I2SPCM3_BGR_REG_I2SPCM3_GATING_OFFSET 0 |

| #define I2SPCM3_BGR_REG_I2SPCM3_GATING_PASS 0b1 |

| #define I2SPCM3_BGR_REG_I2SPCM3_RST_ASSERT 0b0 |

| #define I2SPCM3_BGR_REG_I2SPCM3_RST_CLEAR_MASK 0x00010000 |

| #define I2SPCM3_BGR_REG_I2SPCM3_RST_DE_ASSERT 0b1 |

| #define I2SPCM3_BGR_REG_I2SPCM3_RST_OFFSET 16 |

| #define I2SPCM3_CLK_REG 0x00001230 |

| #define I2SPCM3_CLK_REG_CLK_SRC_SEL_AUDIO0PLL4X 0b000 |

| #define I2SPCM3_CLK_REG_CLK_SRC_SEL_AUDIO1PLL4X 0b001 |

| #define I2SPCM3_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define I2SPCM3_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define I2SPCM3_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b010 |

| #define I2SPCM3_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define I2SPCM3_CLK_REG_FACTOR_M_OFFSET 0 |

| #define I2SPCM3_CLK_REG_SCLK_GATING_CLEAR_MASK 0x80000000 |

| #define I2SPCM3_CLK_REG_SCLK_GATING_CLOCK_IS_OFF 0b0 |

| #define I2SPCM3_CLK_REG_SCLK_GATING_CLOCK_IS_ON 0b1 |

| #define I2SPCM3_CLK_REG_SCLK_GATING_OFFSET 31 |

| #define IOMMU_BGR_REG 0x0000058c |

| #define IOMMU_BGR_REG_IOMMU_GATING_CLEAR_MASK 0x00000001 |

| #define IOMMU_BGR_REG_IOMMU_GATING_MASK 0b0 |

| #define IOMMU_BGR_REG_IOMMU_GATING_OFFSET 0 |

| #define IOMMU_BGR_REG_IOMMU_GATING_PASS 0b1 |

| #define IRRX0_BGR_REG 0x00001004 |

| #define IRRX0_BGR_REG_IRRX0_GATING_CLEAR_MASK 0x00000001 |

| #define IRRX0_BGR_REG_IRRX0_GATING_MASK 0b0 |

| #define IRRX0_BGR_REG_IRRX0_GATING_OFFSET 0 |

| #define IRRX0_BGR_REG_IRRX0_GATING_PASS 0b1 |

| #define IRRX0_BGR_REG_IRRX0_RST_ASSERT 0b0 |

| #define IRRX0_BGR_REG_IRRX0_RST_CLEAR_MASK 0x00010000 |

| #define IRRX0_BGR_REG_IRRX0_RST_DE_ASSERT 0b1 |

| #define IRRX0_BGR_REG_IRRX0_RST_OFFSET 16 |

| #define IRRX0_CLK_REG 0x00001000 |

| #define IRRX0_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define IRRX0_CLK_REG_CLK_SRC_SEL_CLK32K 0b0 |

| #define IRRX0_CLK_REG_CLK_SRC_SEL_HOSC 0b1 |

| #define IRRX0_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define IRRX0_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IRRX0_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IRRX0_CLK_REG_IRRX0_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IRRX0_CLK_REG_IRRX0_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IRRX0_CLK_REG_IRRX0_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IRRX0_CLK_REG_IRRX0_CLK_GATING_OFFSET 31 |

| #define IRRX1_BGR_REG 0x00001104 |

| #define IRRX1_BGR_REG_IRRX1_GATING_CLEAR_MASK 0x00000001 |

| #define IRRX1_BGR_REG_IRRX1_GATING_MASK 0b0 |

| #define IRRX1_BGR_REG_IRRX1_GATING_OFFSET 0 |

| #define IRRX1_BGR_REG_IRRX1_GATING_PASS 0b1 |

| #define IRRX1_BGR_REG_IRRX1_RST_ASSERT 0b0 |

| #define IRRX1_BGR_REG_IRRX1_RST_CLEAR_MASK 0x00010000 |

| #define IRRX1_BGR_REG_IRRX1_RST_DE_ASSERT 0b1 |

| #define IRRX1_BGR_REG_IRRX1_RST_OFFSET 16 |

| #define IRRX1_CLK_REG 0x00001100 |

| #define IRRX1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define IRRX1_CLK_REG_CLK_SRC_SEL_CLK32K 0b0 |

| #define IRRX1_CLK_REG_CLK_SRC_SEL_HOSC 0b1 |

| #define IRRX1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define IRRX1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IRRX1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IRRX1_CLK_REG_IRRX1_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IRRX1_CLK_REG_IRRX1_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IRRX1_CLK_REG_IRRX1_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IRRX1_CLK_REG_IRRX1_CLK_GATING_OFFSET 31 |

| #define IRRX2_BGR_REG 0x0000110c |

| #define IRRX2_BGR_REG_IRRX2_GATING_CLEAR_MASK 0x00000001 |

| #define IRRX2_BGR_REG_IRRX2_GATING_MASK 0b0 |

| #define IRRX2_BGR_REG_IRRX2_GATING_OFFSET 0 |

| #define IRRX2_BGR_REG_IRRX2_GATING_PASS 0b1 |

| #define IRRX2_BGR_REG_IRRX2_RST_ASSERT 0b0 |

| #define IRRX2_BGR_REG_IRRX2_RST_CLEAR_MASK 0x00010000 |

| #define IRRX2_BGR_REG_IRRX2_RST_DE_ASSERT 0b1 |

| #define IRRX2_BGR_REG_IRRX2_RST_OFFSET 16 |

| #define IRRX2_CLK_REG 0x00001108 |

| #define IRRX2_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define IRRX2_CLK_REG_CLK_SRC_SEL_CLK32K 0b0 |

| #define IRRX2_CLK_REG_CLK_SRC_SEL_HOSC 0b1 |

| #define IRRX2_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define IRRX2_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IRRX2_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IRRX2_CLK_REG_IRRX2_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IRRX2_CLK_REG_IRRX2_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IRRX2_CLK_REG_IRRX2_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IRRX2_CLK_REG_IRRX2_CLK_GATING_OFFSET 31 |

| #define IRRX3_BGR_REG 0x00001114 |

| #define IRRX3_BGR_REG_IRRX3_GATING_CLEAR_MASK 0x00000001 |

| #define IRRX3_BGR_REG_IRRX3_GATING_MASK 0b0 |

| #define IRRX3_BGR_REG_IRRX3_GATING_OFFSET 0 |

| #define IRRX3_BGR_REG_IRRX3_GATING_PASS 0b1 |

| #define IRRX3_BGR_REG_IRRX3_RST_ASSERT 0b0 |

| #define IRRX3_BGR_REG_IRRX3_RST_CLEAR_MASK 0x00010000 |

| #define IRRX3_BGR_REG_IRRX3_RST_DE_ASSERT 0b1 |

| #define IRRX3_BGR_REG_IRRX3_RST_OFFSET 16 |

| #define IRRX3_CLK_REG 0x00001110 |

| #define IRRX3_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define IRRX3_CLK_REG_CLK_SRC_SEL_CLK32K 0b0 |

| #define IRRX3_CLK_REG_CLK_SRC_SEL_HOSC 0b1 |

| #define IRRX3_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define IRRX3_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IRRX3_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IRRX3_CLK_REG_IRRX3_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IRRX3_CLK_REG_IRRX3_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IRRX3_CLK_REG_IRRX3_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IRRX3_CLK_REG_IRRX3_CLK_GATING_OFFSET 31 |

| #define IRTX_BGR_REG 0x0000100c |

| #define IRTX_BGR_REG_IRTX_GATING_CLEAR_MASK 0x00000001 |

| #define IRTX_BGR_REG_IRTX_GATING_MASK 0b0 |

| #define IRTX_BGR_REG_IRTX_GATING_OFFSET 0 |

| #define IRTX_BGR_REG_IRTX_GATING_PASS 0b1 |

| #define IRTX_BGR_REG_IRTX_RST_ASSERT 0b0 |

| #define IRTX_BGR_REG_IRTX_RST_CLEAR_MASK 0x00010000 |

| #define IRTX_BGR_REG_IRTX_RST_DE_ASSERT 0b1 |

| #define IRTX_BGR_REG_IRTX_RST_OFFSET 16 |

| #define IRTX_CLK_REG 0x00001008 |

| #define IRTX_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define IRTX_CLK_REG_CLK_SRC_SEL_HOSC 0b0 |

| #define IRTX_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define IRTX_CLK_REG_CLK_SRC_SEL_PERI1_600M 0b1 |

| #define IRTX_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define IRTX_CLK_REG_FACTOR_M_OFFSET 0 |

| #define IRTX_CLK_REG_IRTX_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define IRTX_CLK_REG_IRTX_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define IRTX_CLK_REG_IRTX_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define IRTX_CLK_REG_IRTX_CLK_GATING_OFFSET 31 |

| #define ISP_BGR_REG 0x00001864 |

| #define ISP_BGR_REG_ISP_GATING_CLEAR_MASK 0x00000001 |

| #define ISP_BGR_REG_ISP_GATING_MASK 0b0 |

| #define ISP_BGR_REG_ISP_GATING_OFFSET 0 |

| #define ISP_BGR_REG_ISP_GATING_PASS 0b1 |

| #define ISP_BGR_REG_ISP_RST_ASSERT 0b0 |

| #define ISP_BGR_REG_ISP_RST_CLEAR_MASK 0x00010000 |

| #define ISP_BGR_REG_ISP_RST_DE_ASSERT 0b1 |

| #define ISP_BGR_REG_ISP_RST_OFFSET 16 |

| #define ISP_CLK_REG 0x00001860 |

| #define ISP_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define ISP_CLK_REG_CLK_SRC_SEL_NPUPLL 0b111 |

| #define ISP_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define ISP_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b000 |

| #define ISP_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define ISP_CLK_REG_CLK_SRC_SEL_VEPLL 0b110 |

| #define ISP_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b011 |

| #define ISP_CLK_REG_CLK_SRC_SEL_VIDEO0PLL4X 0b010 |

| #define ISP_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b101 |

| #define ISP_CLK_REG_CLK_SRC_SEL_VIDEO1PLL4X 0b100 |

| #define ISP_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define ISP_CLK_REG_FACTOR_M_OFFSET 0 |

| #define ISP_CLK_REG_ISP_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define ISP_CLK_REG_ISP_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define ISP_CLK_REG_ISP_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define ISP_CLK_REG_ISP_CLK_GATING_OFFSET 31 |

| #define ITS0_BGR_REG 0x00000574 |

| #define ITS0_BGR_REG_ITS0_ACLK_GATING_CLEAR_MASK 0x00000002 |

| #define ITS0_BGR_REG_ITS0_ACLK_GATING_MASK 0b0 |

| #define ITS0_BGR_REG_ITS0_ACLK_GATING_OFFSET 1 |

| #define ITS0_BGR_REG_ITS0_ACLK_GATING_PASS 0b1 |

| #define ITS0_BGR_REG_ITS0_HCLK_GATING_CLEAR_MASK 0x00000001 |

| #define ITS0_BGR_REG_ITS0_HCLK_GATING_MASK 0b0 |

| #define ITS0_BGR_REG_ITS0_HCLK_GATING_OFFSET 0 |

| #define ITS0_BGR_REG_ITS0_HCLK_GATING_PASS 0b1 |

| #define ITS0_BGR_REG_ITS0_RST_ASSERT 0b0 |

| #define ITS0_BGR_REG_ITS0_RST_CLEAR_MASK 0x00010000 |

| #define ITS0_BGR_REG_ITS0_RST_DE_ASSERT 0b1 |

| #define ITS0_BGR_REG_ITS0_RST_OFFSET 16 |

| #define LBC_BGR_REG 0x0000104c |

| #define LBC_BGR_REG_LBC_GATING_CLEAR_MASK 0x00000001 |

| #define LBC_BGR_REG_LBC_GATING_MASK 0b0 |

| #define LBC_BGR_REG_LBC_GATING_OFFSET 0 |

| #define LBC_BGR_REG_LBC_GATING_PASS 0b1 |

| #define LBC_BGR_REG_LBC_RST_ASSERT 0b0 |

| #define LBC_BGR_REG_LBC_RST_CLEAR_MASK 0x00010000 |

| #define LBC_BGR_REG_LBC_RST_DE_ASSERT 0b1 |

| #define LBC_BGR_REG_LBC_RST_OFFSET 16 |

| #define LBC_CLK_REG 0x00001040 |

| #define LBC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define LBC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define LBC_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b010 |

| #define LBC_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define LBC_CLK_REG_CLK_SRC_SEL_PERI0_480M 0b000 |

| #define LBC_CLK_REG_CLK_SRC_SEL_VIDEO0PLL1X 0b011 |

| #define LBC_CLK_REG_CLK_SRC_SEL_VIDEO1PLL3X 0b100 |

| #define LBC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define LBC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define LBC_CLK_REG_FACTOR_N_CLEAR_MASK 0x00001f00 |

| #define LBC_CLK_REG_FACTOR_N_OFFSET 8 |

| #define LBC_CLK_REG_LBC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define LBC_CLK_REG_LBC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define LBC_CLK_REG_LBC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define LBC_CLK_REG_LBC_CLK_GATING_OFFSET 31 |

| #define LBC_NSI_AHB_CLK_REG 0x00001048 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x03000000 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_HOSC 0b00 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_PERI0_200M 0b11 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b10 |

| #define LBC_NSI_AHB_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b01 |

| #define LBC_NSI_AHB_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define LBC_NSI_AHB_CLK_REG_FACTOR_M_OFFSET 0 |

| #define LBC_NSI_AHB_CLK_REG_LBC_NSI_AHB_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define LBC_NSI_AHB_CLK_REG_LBC_NSI_AHB_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define LBC_NSI_AHB_CLK_REG_LBC_NSI_AHB_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define LBC_NSI_AHB_CLK_REG_LBC_NSI_AHB_CLK_GATING_OFFSET 31 |

| #define LEDC_BGR_REG 0x00001704 |

| #define LEDC_BGR_REG_LEDC_GATING_CLEAR_MASK 0x00000001 |

| #define LEDC_BGR_REG_LEDC_GATING_MASK 0b0 |

| #define LEDC_BGR_REG_LEDC_GATING_OFFSET 0 |

| #define LEDC_BGR_REG_LEDC_GATING_PASS 0b1 |

| #define LEDC_BGR_REG_LEDC_RST_ASSERT 0b0 |

| #define LEDC_BGR_REG_LEDC_RST_CLEAR_MASK 0x00010000 |

| #define LEDC_BGR_REG_LEDC_RST_DE_ASSERT 0b1 |

| #define LEDC_BGR_REG_LEDC_RST_OFFSET 16 |

| #define LEDC_CLK_REG 0x00001700 |

| #define LEDC_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x01000000 |

| #define LEDC_CLK_REG_CLK_SRC_SEL_HOSC 0b0 |

| #define LEDC_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define LEDC_CLK_REG_CLK_SRC_SEL_PERI0_600M 0b1 |

| #define LEDC_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define LEDC_CLK_REG_FACTOR_M_OFFSET 0 |

| #define LEDC_CLK_REG_LEDC_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define LEDC_CLK_REG_LEDC_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define LEDC_CLK_REG_LEDC_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define LEDC_CLK_REG_LEDC_CLK_GATING_OFFSET 31 |

| #define LRADC_BGR_REG 0x00001024 |

| #define LRADC_BGR_REG_LRADC_GATING_CLEAR_MASK 0x00000001 |

| #define LRADC_BGR_REG_LRADC_GATING_MASK 0b0 |

| #define LRADC_BGR_REG_LRADC_GATING_OFFSET 0 |

| #define LRADC_BGR_REG_LRADC_GATING_PASS 0b1 |

| #define LRADC_BGR_REG_LRADC_RST_ASSERT 0b0 |

| #define LRADC_BGR_REG_LRADC_RST_CLEAR_MASK 0x00010000 |

| #define LRADC_BGR_REG_LRADC_RST_DE_ASSERT 0b1 |

| #define LRADC_BGR_REG_LRADC_RST_OFFSET 16 |

| #define LVDS0_BGR_REG 0x00001544 |

| #define LVDS0_BGR_REG_LVDS0_RST_ASSERT 0b0 |

| #define LVDS0_BGR_REG_LVDS0_RST_CLEAR_MASK 0x00010000 |

| #define LVDS0_BGR_REG_LVDS0_RST_DE_ASSERT 0b1 |

| #define LVDS0_BGR_REG_LVDS0_RST_OFFSET 16 |

| #define MBUS_CLK_REG 0x00000588 |

| #define MBUS_CLK_REG_MBUS_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define MBUS_CLK_REG_MBUS_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define MBUS_CLK_REG_MBUS_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define MBUS_CLK_REG_MBUS_CLK_GATING_OFFSET 31 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_CLEAR_MASK 0x07000000 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_DDRPLL 0b100 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_HOSC 0b000 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_NPUPLL 0b101 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_OFFSET 24 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_PERI0_400M 0b011 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_PERI0_480M 0b010 |

| #define MBUS_CLK_REG_MBUS_CLK_SEL_PERI0_600M_BUS 0b001 |

| #define MBUS_CLK_REG_MBUS_DFS_EN_CLEAR_MASK 0x10000000 |

| #define MBUS_CLK_REG_MBUS_DFS_EN_DISABLE 0b0 |

| #define MBUS_CLK_REG_MBUS_DFS_EN_ENABLE 0b1 |

| #define MBUS_CLK_REG_MBUS_DFS_EN_OFFSET 28 |

| #define MBUS_CLK_REG_MBUS_DIV1_CLEAR_MASK 0x0000001f |

| #define MBUS_CLK_REG_MBUS_DIV1_OFFSET 0 |

| #define MBUS_CLK_REG_MBUS_UPD_CLEAR_MASK 0x08000000 |

| #define MBUS_CLK_REG_MBUS_UPD_INVALID 0b0 |

| #define MBUS_CLK_REG_MBUS_UPD_OFFSET 27 |

| #define MBUS_CLK_REG_MBUS_UPD_VALID 0b1 |

| #define MBUS_GATE_EN_REG 0x000005e0 |

| #define MBUS_GATE_EN_REG_CAN_MCLK_EN_CLEAR_MASK 0x00020000 |

| #define MBUS_GATE_EN_REG_CAN_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_CAN_MCLK_EN_OFFSET 17 |

| #define MBUS_GATE_EN_REG_CAN_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_CE_MCLK_EN_CLEAR_MASK 0x00000004 |

| #define MBUS_GATE_EN_REG_CE_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_CE_MCLK_EN_OFFSET 2 |

| #define MBUS_GATE_EN_REG_CE_MCLK_EN_SECURE_DEBUG 0b1 |

| #define MBUS_GATE_EN_REG_CSI_MCLK_EN_CLEAR_MASK 0x00000100 |

| #define MBUS_GATE_EN_REG_CSI_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_CSI_MCLK_EN_OFFSET 8 |

| #define MBUS_GATE_EN_REG_CSI_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_DMA0_MCLK_EN_CLEAR_MASK 0x00000001 |

| #define MBUS_GATE_EN_REG_DMA0_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_DMA0_MCLK_EN_OFFSET 0 |

| #define MBUS_GATE_EN_REG_DMA0_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_DMA1_MCLK_EN_CLEAR_MASK 0x00000008 |

| #define MBUS_GATE_EN_REG_DMA1_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_DMA1_MCLK_EN_OFFSET 3 |

| #define MBUS_GATE_EN_REG_DMA1_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_GMAC0_MCLK_EN_CLEAR_MASK 0x00000800 |

| #define MBUS_GATE_EN_REG_GMAC0_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_GMAC0_MCLK_EN_OFFSET 11 |

| #define MBUS_GATE_EN_REG_GMAC0_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_GMAC1_MCLK_EN_CLEAR_MASK 0x00001000 |

| #define MBUS_GATE_EN_REG_GMAC1_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_GMAC1_MCLK_EN_OFFSET 12 |

| #define MBUS_GATE_EN_REG_GMAC1_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_ISP_MCLK_EN_CLEAR_MASK 0x00000200 |

| #define MBUS_GATE_EN_REG_ISP_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_ISP_MCLK_EN_OFFSET 9 |

| #define MBUS_GATE_EN_REG_ISP_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_NAND0_MCLK_EN_CLEAR_MASK 0x00000020 |

| #define MBUS_GATE_EN_REG_NAND0_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_NAND0_MCLK_EN_OFFSET 5 |

| #define MBUS_GATE_EN_REG_NAND0_MCLK_EN_PASS 0b1 |

| #define MBUS_GATE_EN_REG_VE_MCLK_EN_CLEAR_MASK 0x00000002 |

| #define MBUS_GATE_EN_REG_VE_MCLK_EN_MASK 0b0 |

| #define MBUS_GATE_EN_REG_VE_MCLK_EN_OFFSET 1 |

| #define MBUS_GATE_EN_REG_VE_MCLK_EN_PASS 0b1 |

| #define MBUS_MAT_CLK_GATING_REG 0x000005e4 |

| #define MBUS_MAT_CLK_GATING_REG_CAN_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00080000 |

| #define MBUS_MAT_CLK_GATING_REG_CAN_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_CAN_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_CAN_MBUS_GATE_SW_CFG_OFFSET 19 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00040000 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_CE_MBUS_GATE_SW_CFG_OFFSET 18 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC0_MBUS_GATE_SW_CFG_CLEAR_MASK 0x04000000 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC0_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC0_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC0_MBUS_GATE_SW_CFG_OFFSET 26 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC1_MBUS_GATE_SW_CFG_CLEAR_MASK 0x08000000 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC1_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC1_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_GMAC1_MBUS_GATE_SW_CFG_OFFSET 27 |

| #define MBUS_MAT_CLK_GATING_REG_MCU_SYS_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00200000 |

| #define MBUS_MAT_CLK_GATING_REG_MCU_SYS_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_MCU_SYS_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_MCU_SYS_MBUS_GATE_SW_CFG_OFFSET 21 |

| #define MBUS_MAT_CLK_GATING_REG_NAND_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00400000 |

| #define MBUS_MAT_CLK_GATING_REG_NAND_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_NAND_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_NAND_MBUS_GATE_SW_CFG_OFFSET 22 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_CLEAR_MASK 0x01000000 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_NPU_MBUS_GATE_SW_CFG_OFFSET 24 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00020000 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VE_MBUS_GATE_SW_CFG_OFFSET 17 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00100000 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VID_IN_MBUS_GATE_SW_CFG_OFFSET 20 |

| #define MBUS_MAT_CLK_GATING_REG_VO_SYS_MBUS_GATE_SW_CFG_CLEAR_MASK 0x00800000 |

| #define MBUS_MAT_CLK_GATING_REG_VO_SYS_MBUS_GATE_SW_CFG_DISABLE 0b0 |

| #define MBUS_MAT_CLK_GATING_REG_VO_SYS_MBUS_GATE_SW_CFG_ENABLE 0b1 |

| #define MBUS_MAT_CLK_GATING_REG_VO_SYS_MBUS_GATE_SW_CFG_OFFSET 23 |

| #define MSGBOX0_BGR_REG 0x00000744 |

| #define MSGBOX0_BGR_REG_MSGBOX0_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX0_BGR_REG_MSGBOX0_GATING_MASK 0b0 |

| #define MSGBOX0_BGR_REG_MSGBOX0_GATING_OFFSET 0 |

| #define MSGBOX0_BGR_REG_MSGBOX0_GATING_PASS 0b1 |

| #define MSGBOX0_BGR_REG_MSGBOX0_RST_ASSERT 0b0 |

| #define MSGBOX0_BGR_REG_MSGBOX0_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX0_BGR_REG_MSGBOX0_RST_DE_ASSERT 0b1 |

| #define MSGBOX0_BGR_REG_MSGBOX0_RST_OFFSET 16 |

| #define MSGBOX_CORE0_BGR_REG 0x0000074c |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_GATING_MASK 0b0 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_GATING_OFFSET 0 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_GATING_PASS 0b1 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_RST_ASSERT 0b0 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_RST_DE_ASSERT 0b1 |

| #define MSGBOX_CORE0_BGR_REG_MSGBOX_CORE0_RST_OFFSET 16 |

| #define MSGBOX_CORE1_BGR_REG 0x00000754 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_GATING_MASK 0b0 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_GATING_OFFSET 0 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_GATING_PASS 0b1 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_RST_ASSERT 0b0 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_RST_DE_ASSERT 0b1 |

| #define MSGBOX_CORE1_BGR_REG_MSGBOX_CORE1_RST_OFFSET 16 |

| #define MSGBOX_CORE2_BGR_REG 0x0000075c |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_GATING_MASK 0b0 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_GATING_OFFSET 0 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_GATING_PASS 0b1 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_RST_ASSERT 0b0 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_RST_DE_ASSERT 0b1 |

| #define MSGBOX_CORE2_BGR_REG_MSGBOX_CORE2_RST_OFFSET 16 |

| #define MSGBOX_CORE3_BGR_REG 0x00000764 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_GATING_MASK 0b0 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_GATING_OFFSET 0 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_GATING_PASS 0b1 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_RST_ASSERT 0b0 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_RST_DE_ASSERT 0b1 |

| #define MSGBOX_CORE3_BGR_REG_MSGBOX_CORE3_RST_OFFSET 16 |

| #define MSGBOX_RV_BGR_REG 0x0000076c |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_GATING_CLEAR_MASK 0x00000001 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_GATING_MASK 0b0 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_GATING_OFFSET 0 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_GATING_PASS 0b1 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_RST_ASSERT 0b0 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_RST_CLEAR_MASK 0x00010000 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_RST_DE_ASSERT 0b1 |

| #define MSGBOX_RV_BGR_REG_MSGBOX_RV_RST_OFFSET 16 |

| #define NAND0_BGR_REG 0x00000c8c |

| #define NAND0_BGR_REG_NAND0_GATING_CLEAR_MASK 0x00000001 |

| #define NAND0_BGR_REG_NAND0_GATING_MASK 0b0 |

| #define NAND0_BGR_REG_NAND0_GATING_OFFSET 0 |

| #define NAND0_BGR_REG_NAND0_GATING_PASS 0b1 |

| #define NAND0_BGR_REG_NAND0_RST_ASSERT 0b0 |

| #define NAND0_BGR_REG_NAND0_RST_CLEAR_MASK 0x00010000 |

| #define NAND0_BGR_REG_NAND0_RST_DE_ASSERT 0b1 |

| #define NAND0_BGR_REG_NAND0_RST_OFFSET 16 |

| #define NAND0_CLK1_CLK_REG 0x00000c84 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b010 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_PERI1_300M 0b100 |

| #define NAND0_CLK1_CLK_REG_CLK_SRC_SEL_PERI1_400M 0b011 |

| #define NAND0_CLK1_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define NAND0_CLK1_CLK_REG_FACTOR_M_OFFSET 0 |

| #define NAND0_CLK1_CLK_REG_NAND0_CLK1_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define NAND0_CLK1_CLK_REG_NAND0_CLK1_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define NAND0_CLK1_CLK_REG_NAND0_CLK1_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define NAND0_CLK1_CLK_REG_NAND0_CLK1_CLK_GATING_OFFSET 31 |

| #define NAND0_CLK2X_CLK_REG 0x00000c80 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_HOSC 0b000 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_OFFSET 24 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_PERI0_300M 0b010 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_PERI0_400M 0b001 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_PERI1_300M 0b100 |

| #define NAND0_CLK2X_CLK_REG_CLK_SRC_SEL_PERI1_400M 0b011 |

| #define NAND0_CLK2X_CLK_REG_FACTOR_M_CLEAR_MASK 0x0000001f |

| #define NAND0_CLK2X_CLK_REG_FACTOR_M_OFFSET 0 |

| #define NAND0_CLK2X_CLK_REG_NAND0_CLK2X_CLK_GATING_CLEAR_MASK 0x80000000 |

| #define NAND0_CLK2X_CLK_REG_NAND0_CLK2X_CLK_GATING_CLOCK_IS_OFF 0b0 |

| #define NAND0_CLK2X_CLK_REG_NAND0_CLK2X_CLK_GATING_CLOCK_IS_ON 0b1 |

| #define NAND0_CLK2X_CLK_REG_NAND0_CLK2X_CLK_GATING_OFFSET 31 |

| #define NPU_BGR_REG 0x00000b04 |

| #define NPU_BGR_REG_NPU_AHB_RST_ASSERT 0b0 |

| #define NPU_BGR_REG_NPU_AHB_RST_CLEAR_MASK 0x00040000 |

| #define NPU_BGR_REG_NPU_AHB_RST_DE_ASSERT 0b1 |

| #define NPU_BGR_REG_NPU_AHB_RST_OFFSET 18 |

| #define NPU_BGR_REG_NPU_AXI_RST_ASSERT 0b0 |

| #define NPU_BGR_REG_NPU_AXI_RST_CLEAR_MASK 0x00020000 |

| #define NPU_BGR_REG_NPU_AXI_RST_DE_ASSERT 0b1 |

| #define NPU_BGR_REG_NPU_AXI_RST_OFFSET 17 |

| #define NPU_BGR_REG_NPU_CORE_RST_ASSERT 0b0 |

| #define NPU_BGR_REG_NPU_CORE_RST_CLEAR_MASK 0x00010000 |

| #define NPU_BGR_REG_NPU_CORE_RST_DE_ASSERT 0b1 |

| #define NPU_BGR_REG_NPU_CORE_RST_OFFSET 16 |

| #define NPU_BGR_REG_NPU_GATING_CLEAR_MASK 0x00000001 |

| #define NPU_BGR_REG_NPU_GATING_MASK 0b0 |

| #define NPU_BGR_REG_NPU_GATING_OFFSET 0 |

| #define NPU_BGR_REG_NPU_GATING_PASS 0b1 |

| #define NPU_BGR_REG_NPU_GLB_RST_ASSERT 0b0 |

| #define NPU_BGR_REG_NPU_GLB_RST_CLEAR_MASK 0x00080000 |

| #define NPU_BGR_REG_NPU_GLB_RST_DE_ASSERT 0b1 |

| #define NPU_BGR_REG_NPU_GLB_RST_OFFSET 19 |

| #define NPU_BGR_REG_NPU_TZMA_GATING_CLEAR_MASK 0x00000002 |

| #define NPU_BGR_REG_NPU_TZMA_GATING_MASK 0b0 |

| #define NPU_BGR_REG_NPU_TZMA_GATING_OFFSET 1 |

| #define NPU_BGR_REG_NPU_TZMA_GATING_PASS 0b1 |

| #define NPU_CLK_REG 0x00000b00 |

| #define NPU_CLK_REG_CLK_SRC_SEL_CLEAR_MASK 0x07000000 |