|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

Loading...

Searching...

No Matches

|

SyterKit 0.4.0.x

SyterKit is a bare-metal framework

|

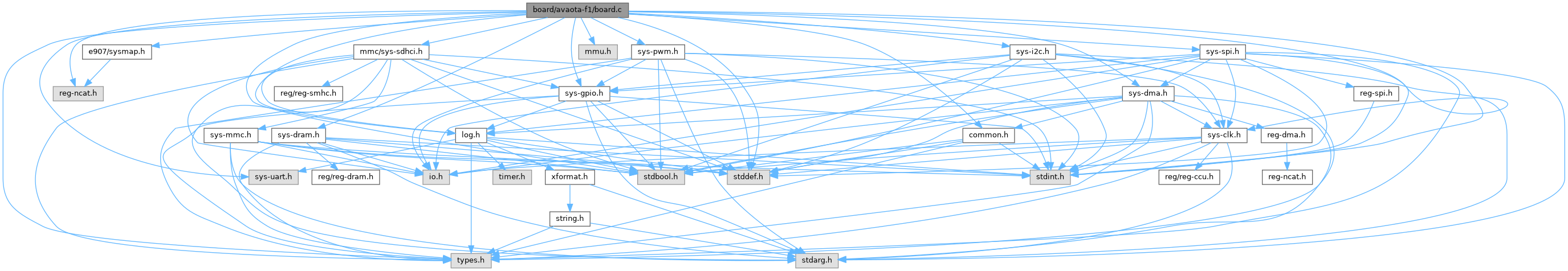

#include <stdbool.h>#include <stddef.h>#include <stdint.h>#include <types.h>#include <log.h>#include <common.h>#include <reg-ncat.h>#include <sys-clk.h>#include <mmu.h>#include <mmc/sys-sdhci.h>#include <sys-dma.h>#include <sys-dram.h>#include <sys-gpio.h>#include <sys-i2c.h>#include <sys-pwm.h>#include <sys-spi.h>#include <sys-uart.h>#include <e907/sysmap.h>

Functions | |

| void | show_chip () |

| int | sunxi_hosc_detect (void) |

| void | sysmap_init (void) |

Variables | |

| sunxi_serial_t | uart_dbg |

| sunxi_serial_t | uart_card |

| sunxi_dma_t | sunxi_dma |

| sunxi_spi_t | sunxi_spi0 |

| sunxi_i2c_t | sunxi_i2c0 |

| sunxi_sdhci_t | sdhci0 |

| sunxi_sdhci_t | sdhci1 |

| sunxi_pwm_channel_t | pwm_channel [] |

| sunxi_pwm_t | pwm_chip0 |

| dram_para_t | dram_para |

| uint8_t | current_hosc_freq |

| Current frequency of the high-speed oscillator (HOSC) in MHz. | |

| void show_chip | ( | ) |

| int sunxi_hosc_detect | ( | void | ) |

| void sysmap_init | ( | void | ) |

|

extern |

Current frequency of the high-speed oscillator (HOSC) in MHz.

| dram_para_t dram_para |

| sunxi_pwm_channel_t pwm_channel[] |

| sunxi_pwm_t pwm_chip0 |

| sunxi_sdhci_t sdhci0 |

| sunxi_sdhci_t sdhci1 |

| sunxi_dma_t sunxi_dma |

| sunxi_i2c_t sunxi_i2c0 |

| sunxi_spi_t sunxi_spi0 |

| sunxi_serial_t uart_card |

| sunxi_serial_t uart_dbg |